## **Table of Contents**

i

**General Information** 8

à

## Contents

| Chapter 1 • Static RAMs              | <br>      | 1 | 1-1         |

|--------------------------------------|-----------|---|-------------|

| Selection Guide                      | <br>      |   | 1-2         |

| IMS1400                              |           |   |             |

| IMS1400L                             |           |   |             |

| IMS1420/21                           |           |   |             |

| IMS1420L                             |           |   |             |

| IMS1423                              |           |   |             |

| IMS1424                              | <br>      | 1 | -43         |

| IMS1403                              |           |   |             |

| IMS1600                              |           |   |             |

| IMS1620                              |           |   |             |

| IMS1624                              |           |   |             |

| IMS1601                              | <br>      | 1 | -62         |

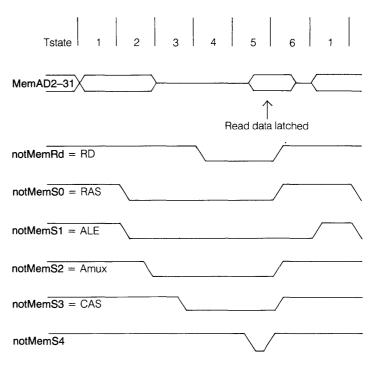

| Chapter 2 • Dynamic RAMs             |           | 2 | 2-1         |

| Selection Guide.                     |           |   |             |

| IMS2600.                             |           |   |             |

| IMS2620.                             |           |   |             |

| IMS2630.                             |           |   |             |

| IMS2800                              |           |   |             |

| IMS2800                              |           |   |             |

|                                      | <br>• • • |   | . 40        |

| Chapter 3 • Military                 | <br>      | 3 | 3-1         |

| Selection Guide.                     | <br>      |   | 3-2         |

| IMS1400M                             |           |   |             |

| IMS1420M                             |           |   |             |

| IMS1423M                             |           |   |             |

| IMS1600M                             |           |   |             |

| IMS1620M                             | <br>      | 3 | 3-35        |

| IMS2600M                             |           |   |             |

|                                      |           |   |             |

| Chapter 4 • Video                    | <br>      | 2 | 4-1         |

| Selection Guide                      |           |   |             |

| IMSG170                              | <br>      |   | 4-3         |

| Chanter E a Troponutor Droducto      |           | E | 5 4         |

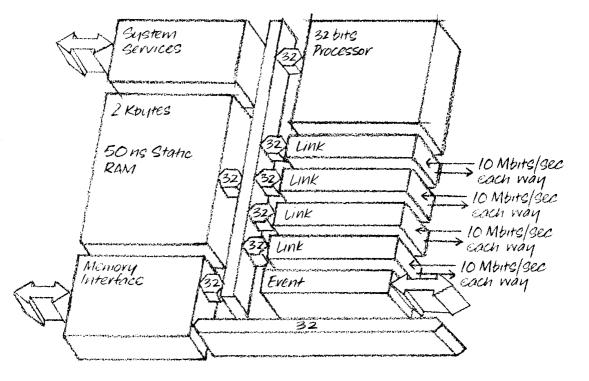

| Chapter 5 • Transputer Products      | <br>      | 🤇 | <b>D-</b> I |

| Selection Guide                      |           |   |             |

| IMS T414 Transputer.                 |           |   |             |

| IMS T212 Transputer                  |           |   |             |

| IMS C001 Link Adaptor.               |           |   |             |

| IMS C002 Link Adaptor.               |           |   |             |

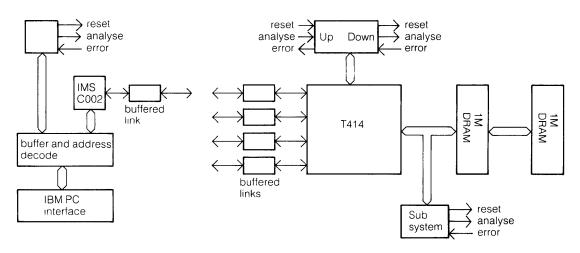

| IMS B001 Evaluation Board.           |           |   |             |

| IMS B002 Evaluation Board.           |           |   |             |

| IMS B004 Evaluation Board.           |           |   |             |

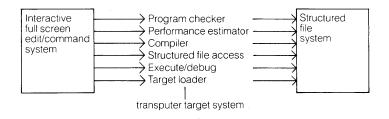

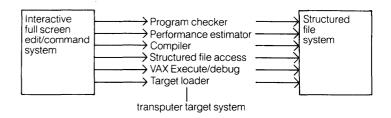

| IMS D100 Development Station.        |           |   |             |

| IMS D600 Development System VAX/VMS. |           |   |             |

| IMS D700 Development System IBM PC   |           |   |             |

|                                      | <br>      |   | -03         |

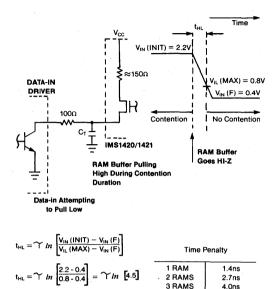

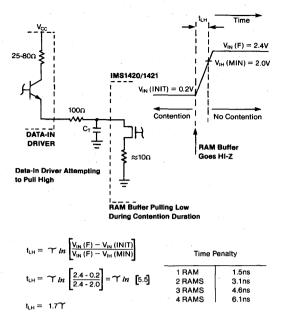

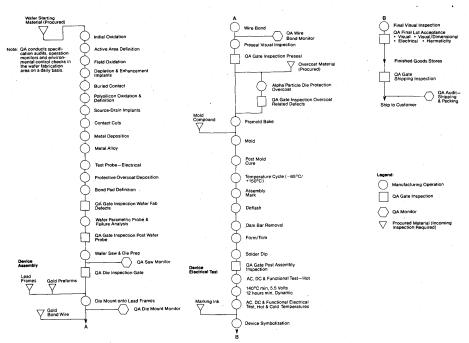

| Chapter 6 • Application Notes.         6           IMS1420, 4Kx4 vs 4Kx1.         IMS1420, 4Kx4 vs 2Kx8.         IMS1400/1420 Bitmaps.         6           IMS2600 Nibble Mode.         6         IMS1420/1421 Bus Contention Considerations.         6 | 6-7<br>6-9<br>6-17 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

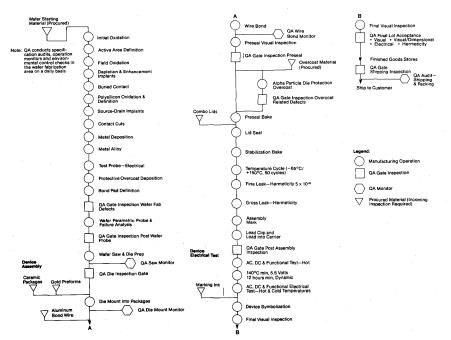

| Chapter 7 • Quality/Reliability                                                                                                                                                                                                                         | 7-1                |

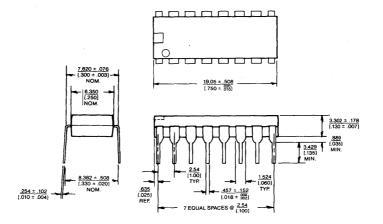

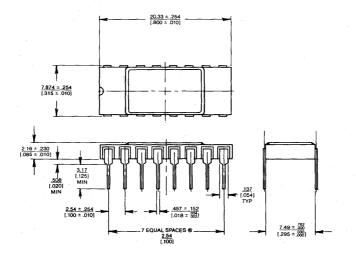

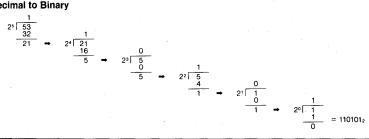

| Chapter 8 • General Information       8         Pin Numbering Scheme       9         Packaging Information       8         Conversion Tables       8         INMOS Sales Offices       8         Representatives       8         Distributors       8   | -13                |

Static RAMs

# Static RAMs 1

4

## **SRAM Selection Guide**

|            |              | Access<br>Times | Maximum C | urrent (mW) | Power           | Number<br>of | Backana         |         |          |

|------------|--------------|-----------------|-----------|-------------|-----------------|--------------|-----------------|---------|----------|

| Device     | Organization | (ns)            | Active    | Standby     | Supply<br>Volts | Pins         | Package<br>Type | Process | Page No. |

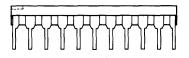

| IMS1400P   | 16K x 1      | 35,45,55        | 660       | 110         | +5              | 20           | ₽∽¥             | NMOS    | 1-3      |

| IMS1400S   | 16K x 1      | 35,45,55        | 660       | 110         | +5              | 20           |                 | NMOS    | 1-3      |

| IMS1400W   | 16K x 1      | 35,45,55        | 660       | 110         | +5              | 20           |                 | NMOS    | 1-3      |

| IMS1400P-L | 16K x 1      | 70,100          | 495       | 83          | +5              | 20           | Р               | NMOS    | 1-11     |

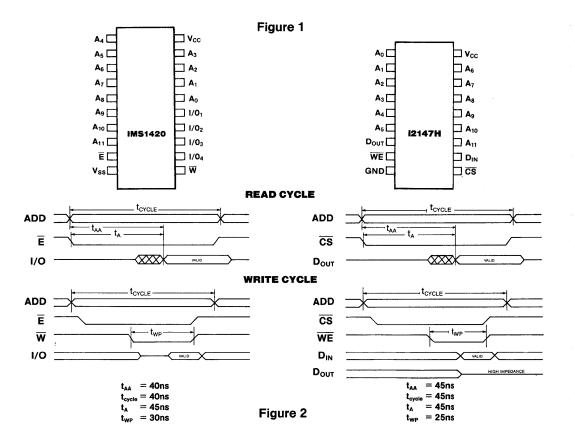

| IMS1420P   | 4K x 4       | 45,55           | 605       | 165         | +5              | 20           | P               | NMOS    | 1-19     |

| IMS1420S   | 4K x 4       | 45,55           | 605       | 165         | +5              | 20           | S               | NMOS    | 1-19     |

| IMS1420W   | 4K x 4       | 45,55           | 605       | 165         | +5              | 20           | W               | NMOS    | 1-19     |

| IMS1421S   | 4K x 4       | 40,50           | 605       | 165         | +5              | 20           | S               | NMOS    | 1-19     |

| IMS1420P-L | 4K x 4       | 70,100          | 495       | 83          | +5              | 20           | Р               | NMOS    | 1-27     |

| IMS1423P   | 4K x 4       | 25,35,45        | 660       | 33 CMOS     | +5              | 20           | P               | CMOS    | 1-35     |

| IMS1423S   | 4K x 4       | 25,35,45        | 660       | 33 CMOS     | +5              | 20           | S               | CMOS    | 1-35     |

| IMS1423W   | 4K x 4       | 25,35,45        | 660       | 33 CMOS     | +5              | 20           | W               | CMOS    | 1-35     |

| IMS1424P   | 4K x 4       | 35,45           | 550       | 33 CMOS     | +5              | 22           | P               | CMOS    | 1-43     |

| IMS1424S   | 4K x 4       | 35,45           | 550       | 33 CMOS     | +5              | 22           | S               | CMOS    | 1-43     |

| IMS1424W   | 4K x 4       | 35,45           | 550       | 33 CMOS     | +5              | 22           | W               | CMOS    | 1-43     |

| IMS1403P   | 16K x 1      | 35,45,55        | 660       | 33 CMOS     | +5              | 20           | P               | CMOS    | 1-44     |

| IMS1403S   | 16K x 1      | 35,45,55        | 660       | 33 CMOS     | +5              | 20           | S               | CMOS    | 1-44     |

| IMS1403W   | 16K x 1      | 35,45,55        | 660       | 33 CMOS     | +5              | 20           | W               | CMOS    | 1-44     |

| IMS1600P   | 64K x 1      | 45,55,70        | 440       | 77 CMOS     | +5              | 22           | P               | CMOS    | 1-45     |

| IMS1600S   | 64K x 1      | 45,55,70        | 440       | 77 CMOS     | +5              | 22           | S               | CMOS    | 1-45     |

| IMS1600W   | 64K x 1      | 45,55,70        | 440       | 77 CMOS     | +5              | 22           | W               | CMOS    | 1-45     |

| IMS1620S   | 16K x 4      | 45,55,70        | 440       | 77 CMOS     | +5              | 22           | S               | CMOS    | 1-53     |

| IMS1620W   | 16K x 4      | 45,55,70        | 440       | 77 CMOS     | +5              | 22           | W               | CMOS    | 1-53     |

| IMS1624S   | 16K x 4      | 45,55,70        | 440       | 77 CMOS     | +5              | 24           | S               | CMOS    | 1-61     |

| IMS1624W   | 16K x 4      | 45,55,70        | 440       | 77 CMOS     | +5              | 28           | W               | CMOS    | 1-61     |

| IMS1601S   | 64K x 1      | 55,70           | 440       | 28 CMOS     | +5              | 22           | S               | CMOS    | 1-62     |

| IMS1601W   | 64K x 1      | 55,70           | 440       | 28 CMOS     | +5              | 22           | W               | CMOS    | 1-62     |

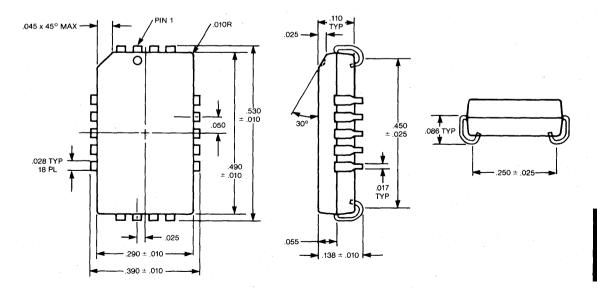

NOTES: P = Plastic DIP S = Ceramic DIP W = Ceramic Chip Carrier

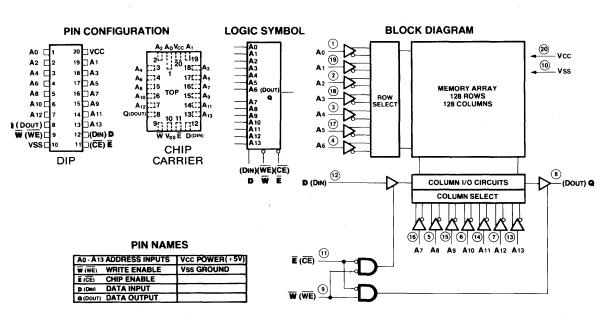

## IMS1400 High Performance 16Kx1 Static RAM

### FEATURES

- 35, 45 and 55ns Chip Enable access

- Maximum active power 660mW

- Maximum standby power 110mW

- Single 5 volt ± 10% supply

- E (CE) power down function

- TTL compatible inputs and output

- Fully static—no clocks for timing

- Three-state output

### DESCRIPTION

The INMOS IMS1400 is a high performance 16K x 1 bit static RAM having access times of 35, 45 and 55ns and a maximum power consumption of 660mW. These

characteristics are made possible by the combination of innovative circuit design and INMOS' proprietary N-MOS technology.

The IMS1400 features fully static operation requiring no external clocks or timing strobes, equal access and cycle times, full TTL compatibility and operation from a single  $\pm 5V \pm 10\%$  power supply. Additionally, a Chip Enable (Ē) function is provided that can be used to place the IMS1400 into a low power standby mode, reducing power consumption to less than 110mW.

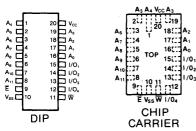

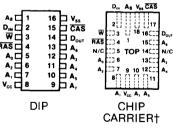

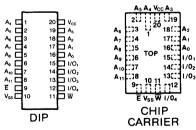

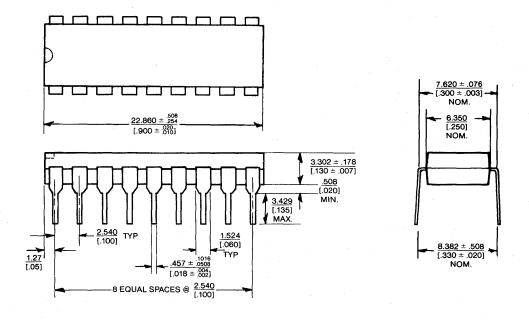

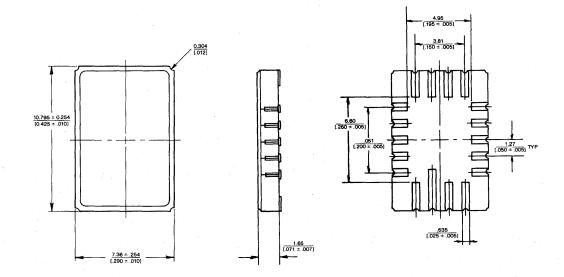

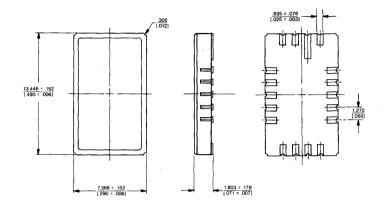

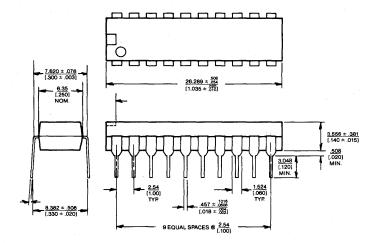

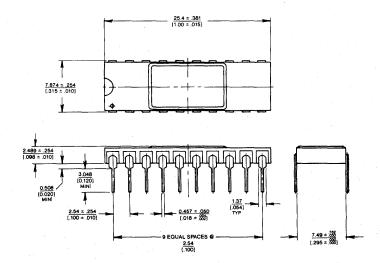

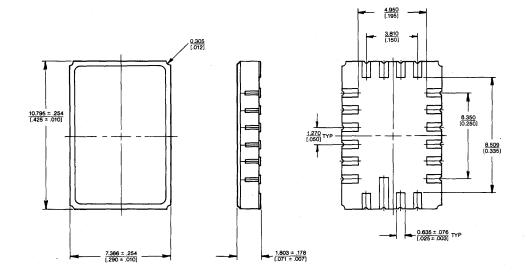

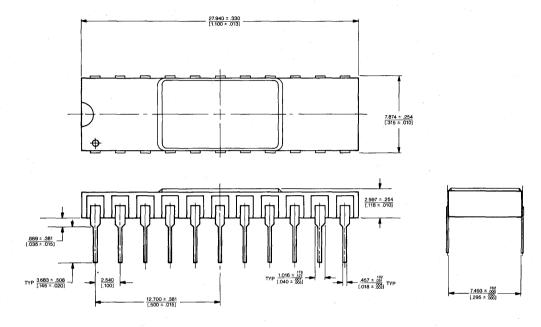

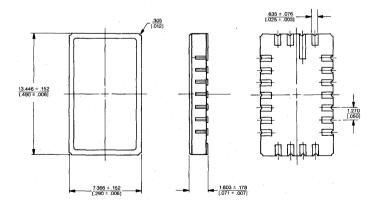

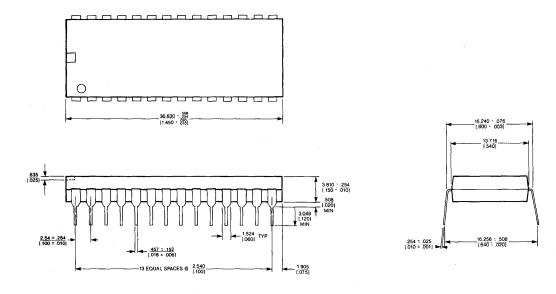

The IMS1400 is packaged in a 20-pin, 300 mil DIP, and is also available in a 20-pin chip carrier, making possible high system packing densities.

The IMS1400 is a high speed VLSI RAM intended for applications that demand superior performance and reliability.

### IMS1400

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to V <sub>ss</sub> | 3.5 to 7.0V    |

|------------------------------------------------|----------------|

| Temperature Under Bias                         | -55°C to 125°C |

| Storage Temp. (Ceramic Package)                | -65°C to 150°C |

| Storage Temp. (Plastic Package)                | -55°C to 125°C |

| Power Dissipation.                             | <i>.</i> 1W    |

| DC Output Current.                             |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **DC OPERATING CONDITIONS**

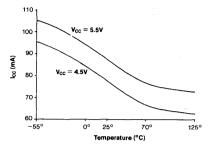

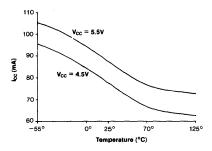

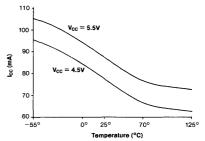

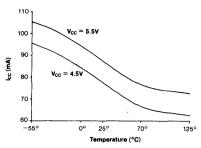

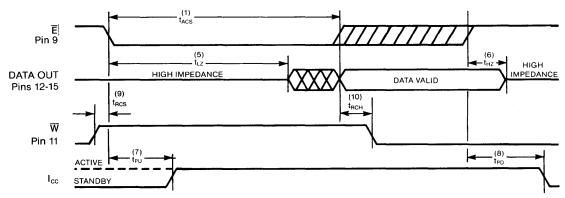

### TYPICAL DYNAMIC ICC VS TEMPERATURE

| SYMBOL          | PARAMETER                     | MIN  | TYP | ΜΑΧ | UNITS | NOTES                                 |

|-----------------|-------------------------------|------|-----|-----|-------|---------------------------------------|

| V <sub>cc</sub> | Supply Voltage                | 4.5  | 5.0 | 5.5 | V     |                                       |

| V <sub>SS</sub> | Supply Voltage                | 0    | 0   | 0   | V     |                                       |

| V <sub>IH</sub> | Input Logic "1" Voltage       | 2.0  |     | 6.0 | ٧     | All Inputs                            |

| VIL             | Input Logic "0" Voltage       | -2.5 |     | 0.8 | ٧     | All Inputs                            |

| T <sub>A</sub>  | Ambient Operating Temperature | 0    |     | 70  | °C    | 400 Linear ft/min transverse air flow |

### DC ELECTRICAL CHARACTERISTICS (0°C $\leq$ T\_A $\leq$ 70°C) (V\_{cc} = 5.0V $\pm$ 10%)

| SYMBOL           | PARAMETER                                        | MIN | МАХ | UNITS | NOTES                                            |

|------------------|--------------------------------------------------|-----|-----|-------|--------------------------------------------------|

| I <sub>CC1</sub> | Average $V_{CC}$ Power Supply Current AC         |     | 120 | mA    | $t_c = t_c \min$                                 |

| I <sub>CC2</sub> | V <sub>cc</sub> Power Supply Current (Standby)   |     | 20  | mA    | $\overline{E} \ge V_{IH}$ min                    |

| I <sub>IN</sub>  | Input Leakage Current (Any Input)                | -10 | 10  | μΑ    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$  |

| Iolk             | Off State Output Leakage Current                 | -50 | 50  | μA    | $V_{cc} = max$<br>$V_{out} = V_{ss}$ to $V_{cc}$ |

| V <sub>OH</sub>  | Output Logic "1" Voltage $I_{OUT} = -4mA$        | 2.4 |     | V     |                                                  |

| V <sub>OL</sub>  | Output Logic "0" Voltage I <sub>OUT</sub> = 16mA |     | 0.4 | V     |                                                  |

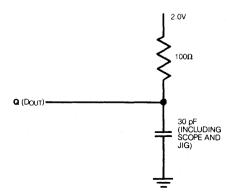

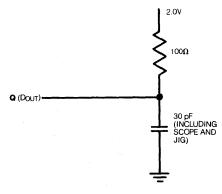

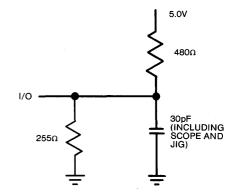

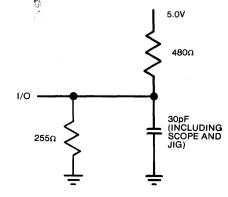

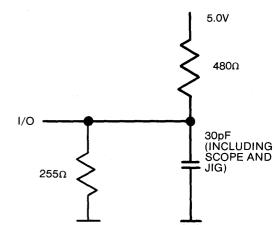

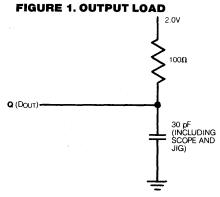

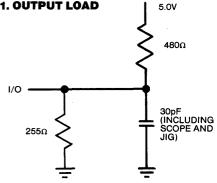

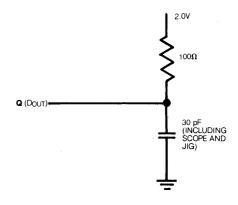

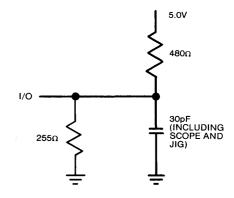

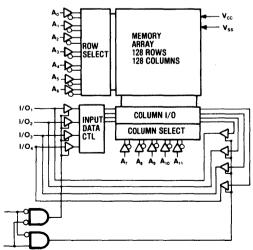

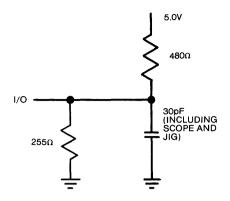

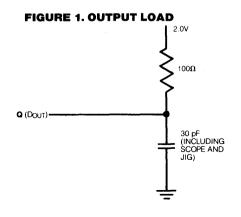

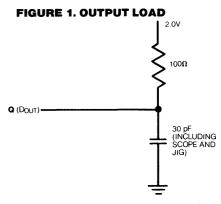

### **AC TEST CONDITIONS**<sup>a</sup>

| Input Pulse Levels                                                                                            |

|---------------------------------------------------------------------------------------------------------------|

| Input Rise and Fall Times 5ns                                                                                 |

| Input and Output Timing Reference Levels 1.5V                                                                 |

| Input Rise and Fall Times. 5ns<br>Input and Output Timing Reference Levels. 1.5V<br>Output Load. See Figure 1 |

Note a: Operation to specifications guaranteed 2ms after  $V_{CC}$  applied.

### **CAPACITANCE** $^{b}$ (T<sub>A</sub> = 25°C, f = 1.0MHz)

| SYMBOL          | BOL PARAMETER      |   | UNIT | CONDITIONS                     |

|-----------------|--------------------|---|------|--------------------------------|

| C <sub>IN</sub> | Input Capacitance  | 4 | pF   | $\Delta V_{\rm c} = 0$ to $3V$ |

| COUT            | Output Capacitance | 7 | pF   | $\Delta V = 0$ to 3V           |

| CE              | E Capacitance      | 6 | pF   | $\Delta V = 0$ to 3V           |

Note b: This parameter is sampled and not 100% tested.

### **FIGURE 1. OUTPUT LOAD**

### RECOMMENDED AC OPERATING CONDITIONS ( $0^{\circ}C \le T_A \le 70^{\circ}C$ ) ( $V_{cc} = 5.0V \pm 10\%$ )

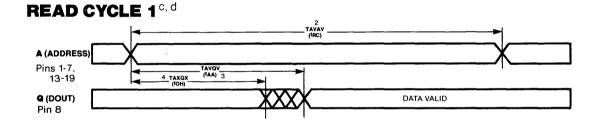

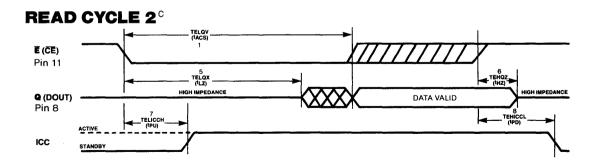

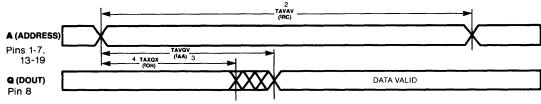

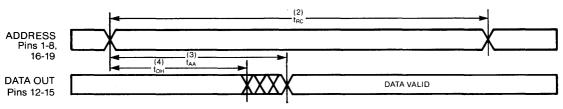

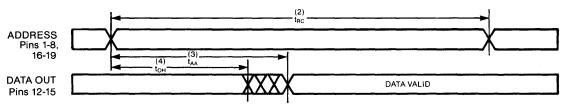

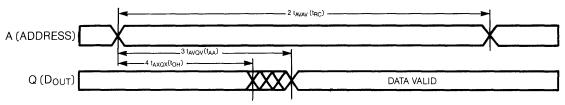

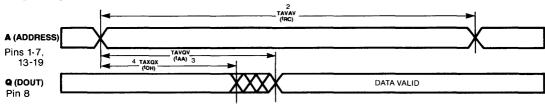

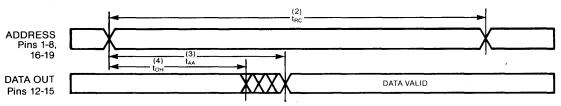

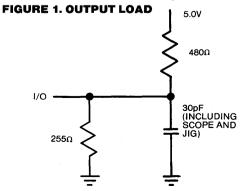

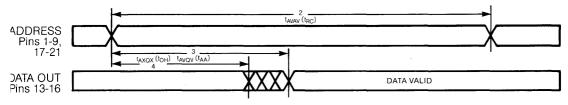

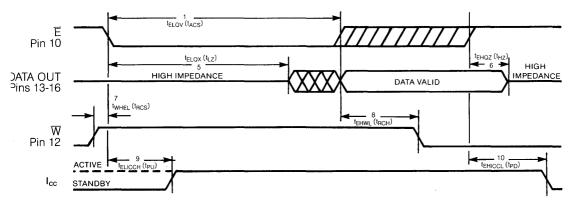

## **READ CYCLE**

| NO.      | SYM                 |                  | PARAMETER                        |     | 0-35 |     | 0-45 |     | 0-55 | UNITS  | NOTES |

|----------|---------------------|------------------|----------------------------------|-----|------|-----|------|-----|------|--------|-------|

| <u>.</u> | Standard            | Alternate        |                                  | MIN | MAX  | MIN | MAX  | MIN | MAX  | 011110 | NOILU |

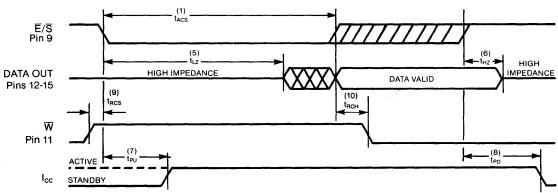

| 1        | t <sub>ELQV</sub>   | t <sub>ACS</sub> | Chip Enable Access Time          |     | 35   |     | 45   |     | 55   | ns     |       |

| 2        | t <sub>avav</sub>   | t <sub>RC</sub>  | Read Cycle Time                  | 35  |      | 40  |      | 50  |      | ns     | С     |

| 3        | t <sub>AVQV</sub>   | t <sub>AA</sub>  | Address Access Time              |     | 35   |     | 40   |     | 50   | ns     | d     |

| 4        | t <sub>AXQX</sub>   | t <sub>он</sub>  | Output Hold After Address Change | 3   |      | 3   |      | 3   |      | ns     |       |

| 5        | t <sub>ELQX</sub>   | t <sub>LZ</sub>  | Chip Enable to Output Active     | 5   |      | 5   |      | 5   |      | ns     |       |

| 6        | t <sub>EHQZ</sub>   | t <sub>HZ</sub>  | Chip Disable to Output Disable   | 0   | 25   | 0   | 25   | 0   | 30   | ns     | f     |

| 7        | t <sub>ELICCH</sub> | t <sub>PU</sub>  | Chip Enable to Power Up          | 0   |      | 0   |      | 0   |      | ns     |       |

| 8        | t <sub>EHICCL</sub> | t <sub>PD</sub>  | hip Disable to Power Down        |     | 45   | 0   | 45   | 0   | 55   | ns     |       |

|          |                     | t <sub>T</sub>   | Input Rise and Fall Times        |     | 50   |     | 50   |     | 50   | ns     | е     |

Note c: For READ CYCLES 1 & 2,  $\overline{W}$  is high for entire cycle.

Note d: Device is continuously selected  $\overline{E}$  low.

Note e: Measured between  $V_{IL}$  max and  $V_{IH}$  min. Note f: Measured  $\pm$  200mV from steady state output voltage.

| NO. |                   | BOL              | PARAMETER                            |     | 0-35 |     | 0-45 |     | 0-55 | PINITS | NOTES |

|-----|-------------------|------------------|--------------------------------------|-----|------|-----|------|-----|------|--------|-------|

|     | Standard          | Alternate        | TANAMETEN                            | MIN | MAX  | MIN | MAX  | MIN | MAX  | UNITS  | NOILS |

| 9   | t <sub>AVAV</sub> | t <sub>wc</sub>  | Write Cycle Time                     |     |      | 40  |      | 50  |      | ns     |       |

| 10  | t <sub>wLWH</sub> | t <sub>wP</sub>  | Write Pulse Width                    |     |      | 20  |      | 25  |      | ns     |       |

| 11  | t <sub>elwh</sub> | t <sub>cw</sub>  | Chip Enable to End of Write          | 35  |      | 40  |      | 50  |      | ns     |       |

| 12  | t <sub>DVWH</sub> | t <sub>DW</sub>  | Data Set-up to End of Write          | 15  |      | 15  |      | 20  |      | ns     |       |

| 13  | t <sub>wHDX</sub> | t <sub>DH</sub>  | Data Hold After End of Write         |     |      | 0   |      | 0   |      | ns     |       |

| 14  | t <sub>avwh</sub> | t <sub>AW_</sub> | Address Set-up to End of Write       | 35  |      | 40  |      | 50  |      | ns     |       |

| 15  | t <sub>AVWL</sub> | t <sub>AS</sub>  | Address Set-up to Beginning of Write | 10  |      | 10  |      | 15  |      | ns     |       |

| 16  | t <sub>whax</sub> | t <sub>wR</sub>  | Address Hold After End of Write      |     |      | 0   |      | 0   |      | ns     |       |

| 17  | t <sub>wLQZ</sub> | t <sub>wz</sub>  | Write Enable to Output Disable       |     | 20   | 0   | 20   | 0   | 25   | ns     | f     |

| 18  | t <sub>wHQX</sub> | t <sub>ow</sub>  | Output Active After End of Write     |     | 25   | 0   | 25   | 0   | 30   | ns     | g     |

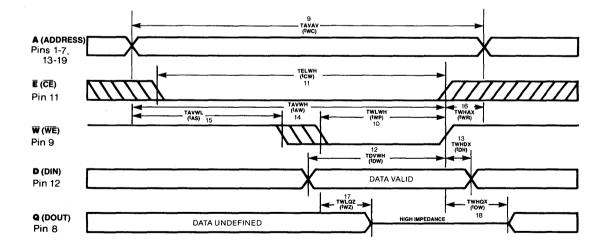

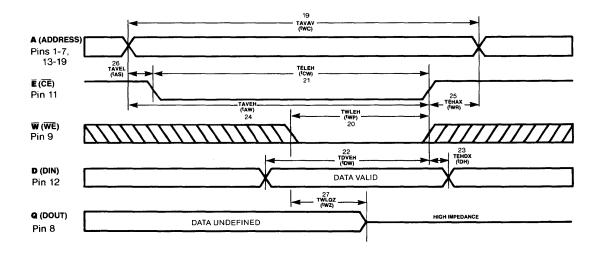

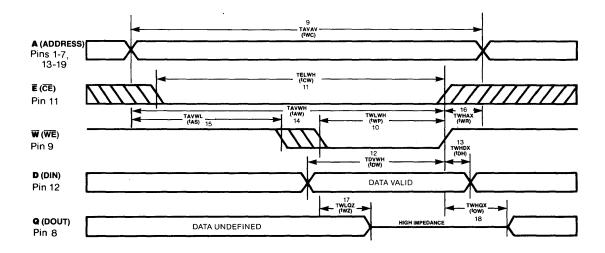

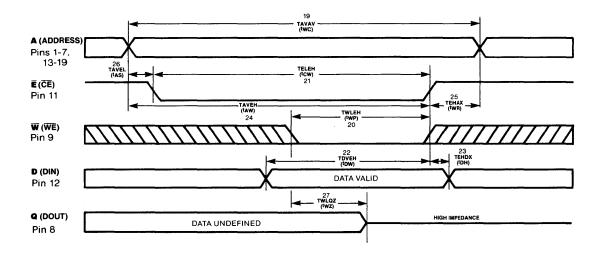

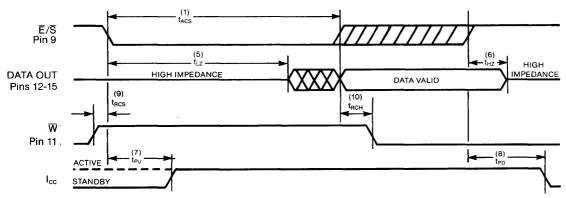

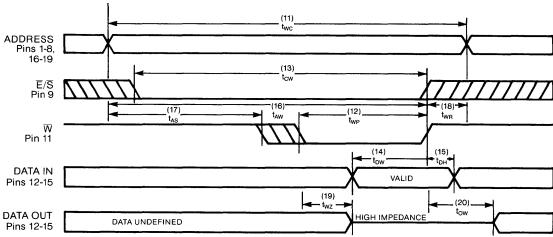

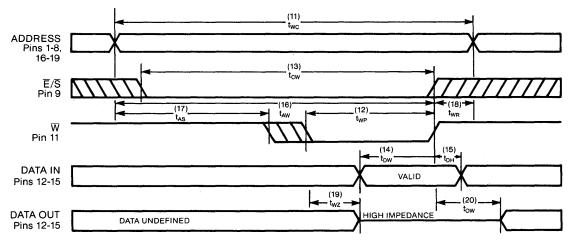

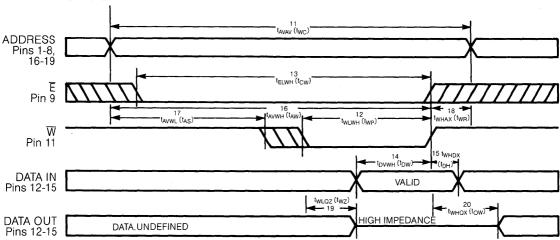

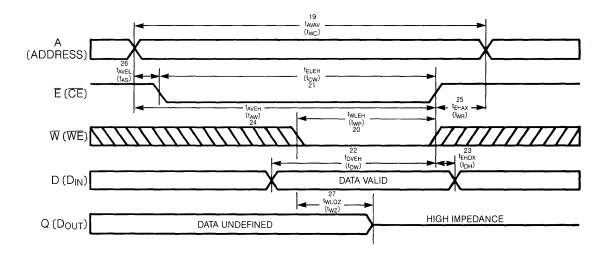

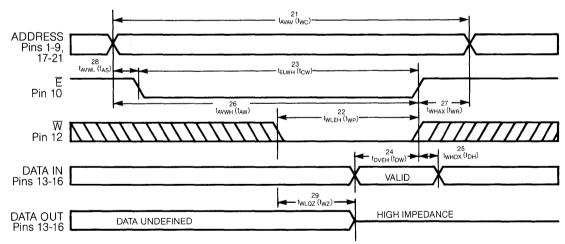

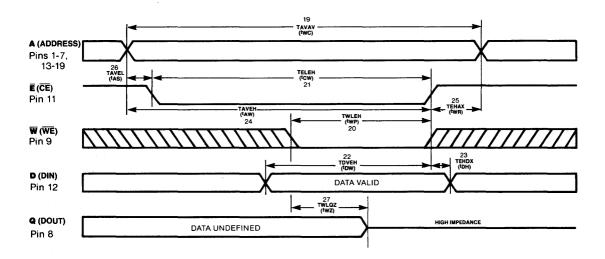

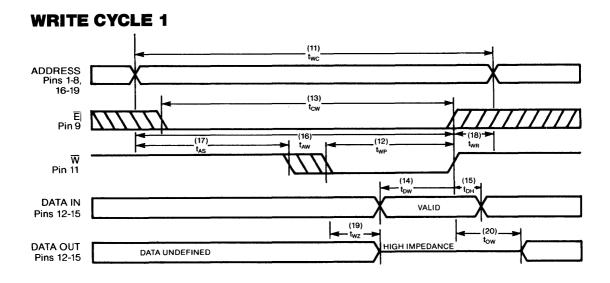

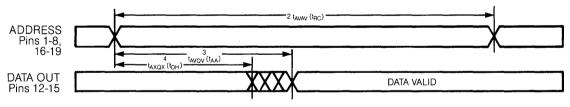

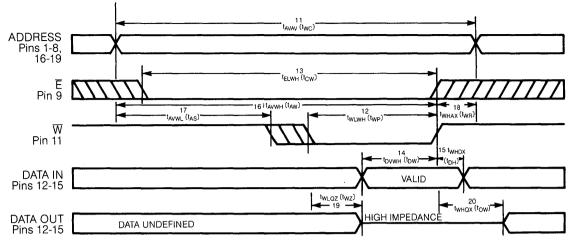

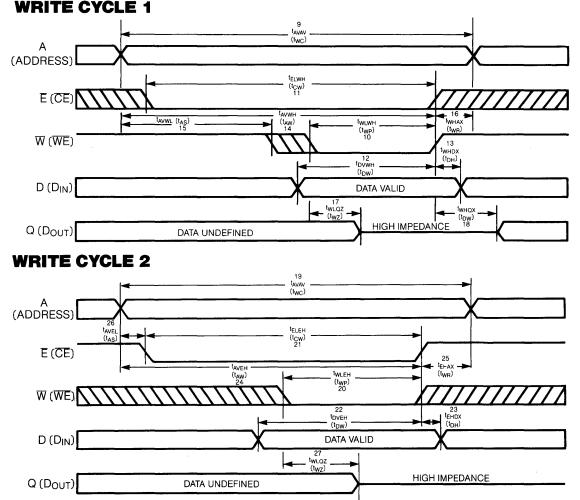

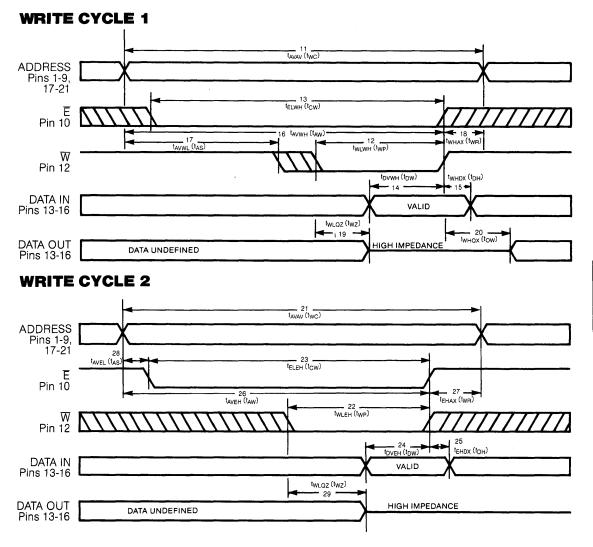

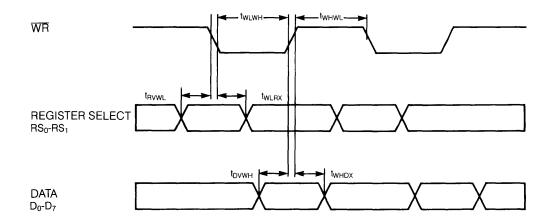

## WRITE CYCLE 1: W CONTROLLED<sup>h</sup>

Note f: Measured ± 200mV from steady state output voltage. Note g: If  $\overline{E}$  goes low with  $\overline{W}$  low, output remains in high impedance state. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{IH}$  during address transition.

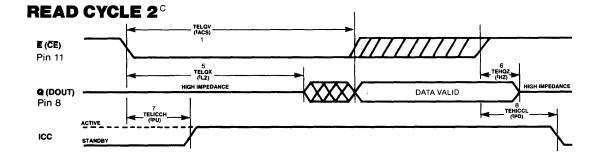

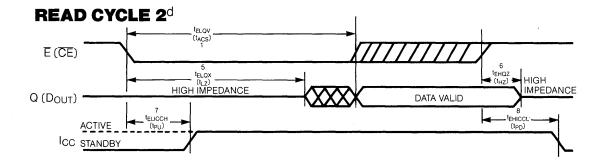

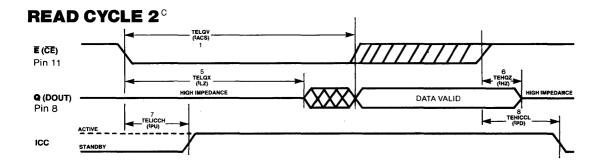

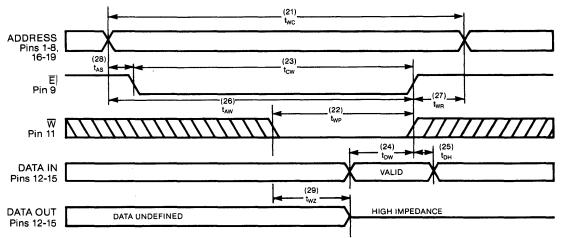

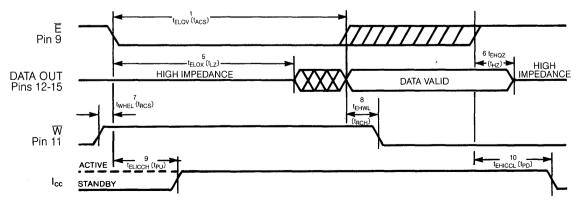

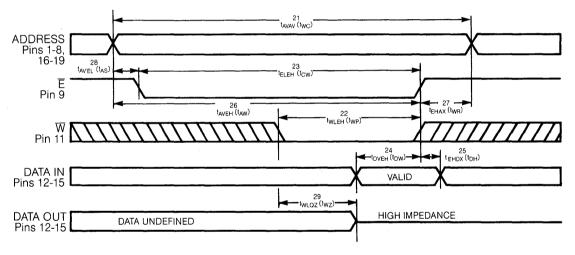

## WRITE CYCLE 2: E CONTROLLED<sup>h</sup>

| NO.      |                   | BOL             | PARAMETER                            |     | 0-35 |     | 0-45 |     | 0-55 | UNITS | NOTES |

|----------|-------------------|-----------------|--------------------------------------|-----|------|-----|------|-----|------|-------|-------|

| <u> </u> | Standard          | Alternate       |                                      | MIN | MAX  | MIN | MAX  | MIN | MAX  |       | NOTEO |

| 19       | t <sub>AVAV</sub> | t <sub>wc</sub> | Write Cycle Time                     |     |      | 40  |      | 50  |      | ns    |       |

| 20       | t <sub>wLEH</sub> | t <sub>wP</sub> | Write Pulse Width                    |     |      | 20  |      | 25  |      | ns    |       |

| 21       | t <sub>elen</sub> | t <sub>CW</sub> | Chip Enable to End of Write          |     |      | 40  |      | 50  |      | ns    |       |

| 22       | t <sub>DVEH</sub> | t <sub>DW</sub> | Data Set-up to End of Write          |     |      | 15  |      | 20  |      | ns    |       |

| 23       | t <sub>endx</sub> | t <sub>DH</sub> | Data Hold After End of Write         | 5   |      | 5   |      | 5   |      | ns    |       |

| 24       | t <sub>AVEH</sub> | t <sub>AW</sub> | Address Set-up to End of Write       | 35  |      | 40  |      | 50  |      | ns    |       |

| 25       | t <sub>EHAX</sub> | t <sub>wR</sub> | Address Hold After End of Write      |     |      | 0   |      | 0   |      | ns    |       |

| 26       | t <sub>AVEL</sub> | t <sub>AS</sub> | Address Set-up to Beginning of Write |     |      | -5  |      | -5  |      | ns    |       |

| 27       | t <sub>wLQZ</sub> | t <sub>wz</sub> | Write Enable to Output Disable 0     |     | 20   | 0   | 20   | 0   | 25   | ns    | f     |

Note f: Measured  $\pm$  200mV from steady state output voltage. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq$  V<sub>IH</sub> during address transitions.

### IMS1400

### **DEVICE OPERATION**

The IMS1400 has two control inputs, Chip Enable (E) and Write Enable (W), fourteen address inputs, a data in ( $D_{IN}$ ) and a data out ( $D_{OUT}$ ).

When  $V_{CC}$  is first applied to pin 20, a circuit associated with the  $\overline{E}$  input forces the device into the lower power standby mode regardless of the state of the  $\overline{E}$  input. After  $V_{CC}$  is applied for 2ms, the  $\overline{E}$  input controls device selection as well as active and standby modes.

With  $\overline{E}$  low, the device is selected and the 14 address inputs are decoded to select one memory cell out of 16,385. READ and WRITE operations on the memory cell are controlled by  $\overline{W}$  input. With  $\overline{E}$  high, the device is deselected, the output is disabled, and the power consumption is reduced to less than 1/6 of the active mode power.

#### **READ CYCLE**

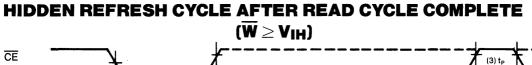

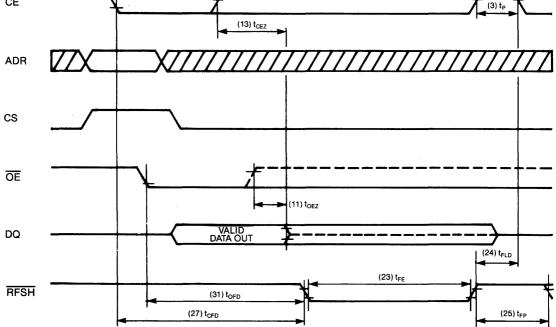

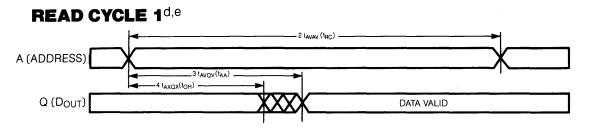

A read cycle is defined as  $\overline{W} \geq V_{iH}$  min with  $\overline{E} \leq V_{iL}$  max. Read access time is measured from either  $\overline{E}$  going low or from valid address.

The READ CYCLE 1 waveform on page 3 shows a read access that is initiated by a change in the address inputs while  $\overline{E}$  is low. The output remains active throughout a READ CYCLE 1 and is valid at the specified address access time. As long as  $\overline{E}$  remains low, the cycle time is equal to the address access time.

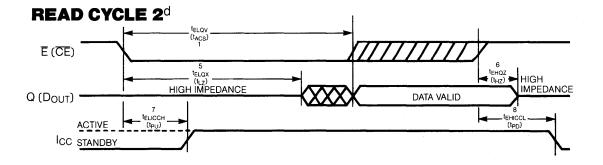

The READ CYCLE 2 waveform on page 3 shows a read access that is initiated by  $\overline{E}$  going low. As long as address is stable within 5ns after  $\overline{E}$  goes low, valid data is at the output at the specified Chip Enable access time. If address is not valid within 5ns after  $\overline{E}$  goes low,

the timing is as specified in the READ CYCLE 1. Chip Enable access time is not affected by the duration of the deselect interval.

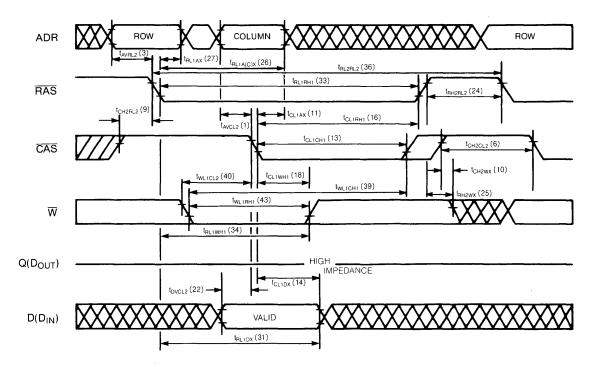

#### WRITE CYCLE

A write cycle is initiated by the latter of  $\overline{W}$  or  $\overline{E}$  going low, and terminated by  $\overline{W}$  (WRITE CYCLE 1) or  $\overline{E}$ (WRITE CYCLE 2) going high. During the write cycle, data on the input ( $D_{IN}$ ) is written into the selected cell, and the output ( $D_{OUT}$ ) is in high impedance.

If a write cycle is initiated by  $\overline{W}$  going low, the address must be stable for the WRITE CYCLE 1 set-up time. If a write cycle is initiated by  $\overline{E}$  going low, the address must be held stable for the entire write cycle. After  $\overline{W}$ or  $\overline{E}$  goes high to terminate the cycle, addresses may change. If these address set-up and hold times are not met, contents of other cells may be altered in unpredictable ways.

WRITE CYCLE 1 waveform on page 4 shows a write cycle terminated by  $\overline{W}$  going high.  $D_{\text{IN}}$  set-up and hold times are referenced to the rising edge of  $\overline{W}$ . With  $\overline{W}$  high,  $D_{\text{OUT}}$  becomes active.

WRITE CYCLE 2 waveform on page 5 shows a write cycle terminated by  $\overline{E}$  going high. D<sub>IN</sub> set-up and hold times are referenced to the rising edge of  $\overline{E}$ . With  $\overline{E}$  high, D<sub>OUT</sub> remains in the high impedance state.

### **APPLICATION**

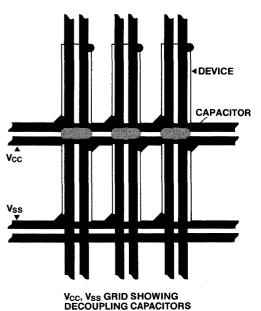

To ensure proper operation of the IMS1400 in a system environment, it is recommended that the following guidelines on board layout and power distribution be followed.

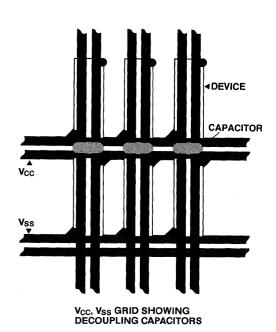

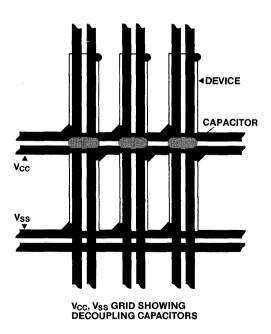

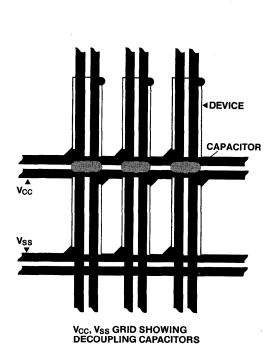

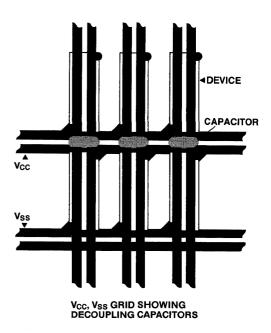

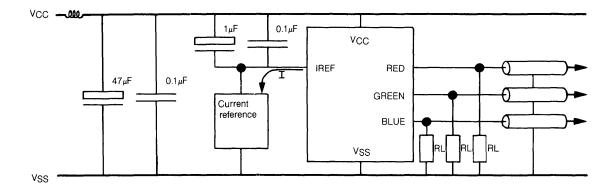

### POWER DISTRIBUTION

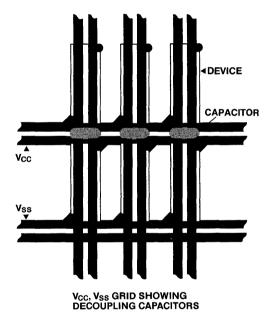

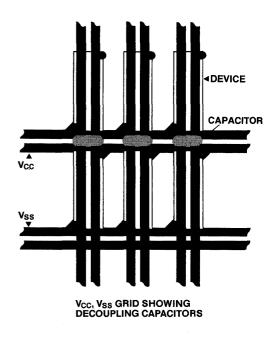

The recommended power distribution scheme combines proper power trace layout and placement of decoupling capacitors. The impedance in the decoupling path from the power pin (20) through the decoupling capacitor, to the ground pin (10) should be kept to a minimum. The impedance of this path is determined by the series impedance of the power line inductance and the inductance and reactance of the decoupling capacitor.

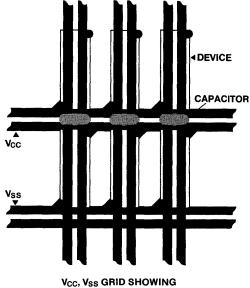

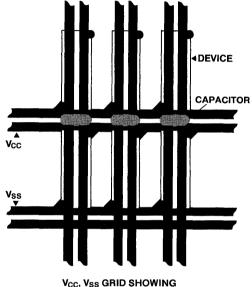

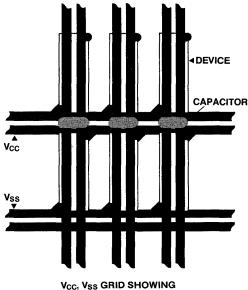

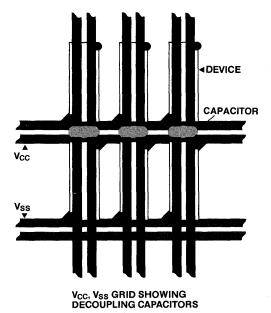

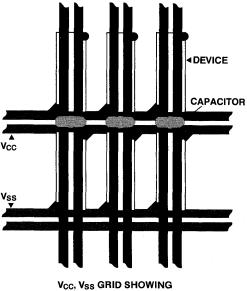

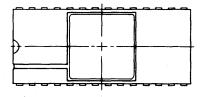

To reduce the power line impedance, it is recommended that the power trace and ground trace be gridded or provided by separate power planes. The high frequency decoupling capacitor should have a value of  $0.1\mu$ F, and be placed between the rows of memory devices in the array (see drawing). A larger tantalum

DECOUPLING CAPACITORS

capacitor with a value between  $22\mu$ F and  $47\mu$ F should be placed near the memory board edge connection where the power traces meet the backplane power distribution system. These large capacitors provide bulk energy storage to prevent voltage drop due to the main supply being located off the memory board and at the end of a long inductive path.

Also, to prevent loss of signal margins due to differential ground noise, the ground grid of the memory array should be extended to the TTL drivers in the peripheral circuitry.

### TERMINATION

Trace lines on a memory board in the array look to TTL driver signals like low impedance, unterminated transmission lines. In order to reduce or eliminate the reflections of the TTL signals, line termination is recommended. The termination may be either parallel or series but the series termination technique has the advantages of drawing no DC current and using a minimum of components. The recommended technique is to use series termination.

A series resistor in the signal line at the output of the TTL driver to match the source impedance of the TTL driver to the signal line will dampen the reflections on the line. The line should be kept short with the driver-termination combination close to the memory array.

Some experimentation will have to be done to find the proper value to use for the series termination to minimize reflections, but generally a series resistor in the  $10\Omega$  to  $30\Omega$  range will be required.

The use of proper power distribution techniques, including adequate use of decoupling capacitors, along with proper termination of TTL driver outputs, are some of the most important, yet basic rules to be followed.

The rules are intended to maintain the operating margins of all devices on the memory board by providing a quiet environment relatively free of noise spikes and signal reflections. **IMS1400**

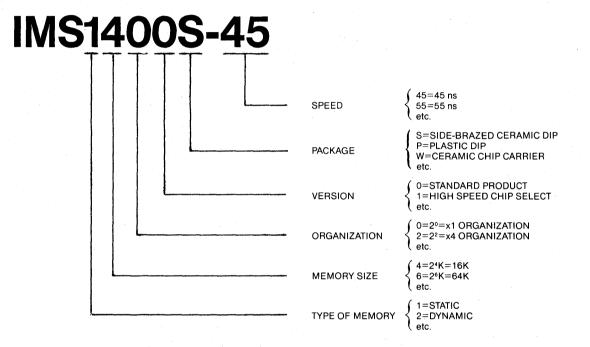

### **ORDERING INFORMATION**

| DEVICE  | SPEED                                                                | PACKAGE                                                                                                                           | PART NUMBER                                                                                                                         |

|---------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| IMS1400 | <b>SPEED</b><br>35ns<br>35ns<br>45ns<br>45ns<br>45ns<br>55ns<br>55ns | PACKAGE<br>PLASTIC DIP<br>CERAMIC DIP<br>CHIP CARRIER<br>PLASTIC DIP<br>CERAMIC DIP<br>CHIP CARRIER<br>PLASTIC DIP<br>CERAMIC DIP | PART NUMBER<br>IMS1400P-35<br>IMS1400W-35<br>IMS1400W-35<br>IMS1400P-45<br>IMS1400W-45<br>IMS1400W-45<br>IMS1400P-55<br>IMS1400S-55 |

|         | 55ns                                                                 | CHIP CARRIER                                                                                                                      | IMS1400W-55                                                                                                                         |

## IMS1400L Low Power 16Kx1 Static RAM

### FEATURES

- 70 and 100ns Chip Enable access

- Maximum active power 495mW

- Maximum standby power 83mW

- Single 5 volt ± 10% supply

- E power down function

- TTL compatible inputs and output

- Fully static no clocks for timing

- Three-state output

### DESCRIPTION

The INMOS IMS1400L is a high performance 16K x 1 bit static RAM having access time of 70 and 100ns and a maximum power consumption of 495mW. These

characteristics are made possible by the combination of innovative circuit design and INMOS' proprietary N-MOS technology.

The IMS1400L features fully static operation requiring no external clocks or timing strobes, equal access and cycle times, full TTL compatibility and operation from a single  $\pm 5V \pm 10\%$  power supply. Additionally, a Chip Enable (Ē) function is provided that can be used to place the IMS1400L into a low power standby mode, reducing power consumption to less than 83mW.

The IMS1400L is packaged in a 20-pin, 300-mil plastic DIP, making possible high system packing densities.

The IMS1400L is a high speed VLSI RAM intended for low power applications that demand superior performance and reliability.

### IMS1400L

## TYPICAL DYNAMIC ICC VS TEMPERATURE

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to V <sub>ss</sub> | 3.5 to 7.0V    |

|------------------------------------------------|----------------|

| Temperature Under Bias                         | -55°C to 125°C |

| Storage Temperature (Ambient)                  |                |

| Power Dissipation.                             | 1W             |

| DC Output Current.                             |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **DC OPERATING CONDITIONS**

| SYMBOL          | PARAMETER                     | MIN  | TYP | ΜΑΧ | UNITS | NOTES                                 |

|-----------------|-------------------------------|------|-----|-----|-------|---------------------------------------|

| V <sub>cc</sub> | Supply Voltage                | 4.5  | 5.0 | 5.5 | V     |                                       |

| V <sub>SS</sub> | Supply Voltage                | 0    | 0   | 0   | ٧     |                                       |

| V <sub>iH</sub> | Input Logic "1" Voltage       | 2.0  |     | 6.0 | ۷     |                                       |

| V <sub>IL</sub> | Input Logic "0" Voltage       | -2.0 |     | 0.8 | V     |                                       |

| T <sub>A</sub>  | Ambient Operating Temperature | 0    |     | 70  | °C    | 400 Linear ft/min transverse air flow |

### DC ELECTRICAL CHARACTERISTICS ( $0^{\circ}C \le T_{A} \le 70^{\circ}C$ ) ( $V_{CC} = 5.0V \pm 10\%$ )

|                  |                                                   |          |     | r   |       |                                                  |

|------------------|---------------------------------------------------|----------|-----|-----|-------|--------------------------------------------------|

| SYMBOL           | PARAMETER                                         |          | MIN | MAX | UNITS | NOTES                                            |

| I <sub>CC1</sub> | Average V <sub>cc</sub> Power                     | 0°C      |     | 90  |       |                                                  |

|                  | Supply Current AC                                 | 25°C     |     | 85  | mA    | $t_c = t_c min$                                  |

|                  |                                                   | 70°C     |     | 75  |       |                                                  |

| I <sub>CC2</sub> | V <sub>CC</sub> Power Supply Current<br>(Standby) | 0°C-70°C |     | 15  | mA    | $\overline{E} \ge V_{iH}$ min                    |

| I <sub>IN</sub>  | Input Leakage Current<br>(Any Input)              |          | -10 | 10  | μΑ    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$  |

| I <sub>olk</sub> | Off State Output<br>Leakage Current               |          | -50 | 50  | μA    | $V_{cc} = max$<br>$V_{out} = V_{ss}$ to $V_{cc}$ |

| V <sub>OH</sub>  | Output Logic "1" Voltage $I_{OUT} = -4mA$         |          | 2.4 |     | V     |                                                  |

| V <sub>OL</sub>  | Output Logic "0" Voltage I <sub>OUT</sub> =       | 16mA     |     | 0.4 | V     |                                                  |

### **AC TEST CONDITIONS**<sup>a</sup>

| Input Pulse Levels |

|--------------------|

| Output Load        |

Note a: Operation to specifications guaranteed 2ms after V<sub>CC</sub> applied.

### **CAPACITANCE**<sup>b</sup> ( $T_A = 25^{\circ}C$ , f = 1.0MHz)

| SYMBOL | PARAMETER          | MAX | UNIT | CONDITIONS           |  |  |

|--------|--------------------|-----|------|----------------------|--|--|

| CIN    | Input Capacitance  | 4   | pF   | $\Delta V = 0$ to 3V |  |  |

| COUT   | Output Capacitance | 7   | pF   | $\Delta V = 0$ to 3V |  |  |

| CE     | E Capacitance      | 6   | рF   | $\Delta V = 0$ to 3V |  |  |

Note b: This parameter is sampled and not 100% tested.

### **FIGURE 1. OUTPUT LOAD**

## **READ CYCLE**

| NO.  | SYMBOL           | PARAMETER                        | 1420 | L-70 | 1420L-10 |     | UNITS | NOTES |

|------|------------------|----------------------------------|------|------|----------|-----|-------|-------|

| 110. | UTINDUL          |                                  | MIN  | MAX  | MIN      | MAX |       | NOILO |

| 1    | t <sub>ACS</sub> | Chip Enable Access Time          |      | 70   |          | 100 | ns    |       |

| 2    | t <sub>RC</sub>  | Read Cycle Time                  | 65   |      | 95       |     | ns    | с     |

| 3    | t <sub>AA</sub>  | Address Access Time              |      | 65   |          | 95  | ns    | d     |

| 4    | t <sub>он</sub>  | Output Hold After Address Change | 5    |      | 5        |     | ns    |       |

| 5    | t <sub>LZ</sub>  | Chip Enable to Output Active     | 20   |      | 20       |     | ns    |       |

| 6    | t <sub>HZ</sub>  | Chip Disable to Output Disable   |      | 25   |          | 25  | ns    | f     |

| 7    | t <sub>PU</sub>  | Chip Enable to Power Up          | 0    |      | 0        |     | ns    |       |

| 8    | t <sub>PD</sub>  | Chip Disable to Power Down       |      | 70   |          | 70  | ns    |       |

| 9    | t <sub>RCS</sub> | Read Command Set-up Time         | -5   |      | -5       |     | ns    |       |

| 10   | t <sub>RCH</sub> | Read Command Hold Time           | -5   |      | -5       |     | ns    |       |

|      | t <sub>T</sub>   | Input Rise and Fall Times        |      | 50   |          | 50  | ns    | е     |

Note c: For READ CYCLE 1 & 2,  $\overline{W}$  is high for entire cycle.

Note d: Device is continuously selected  $\breve{E}$  low.

Note e: Measured between  $V_{IL}$  max and  $V_{IH}$  min.

Note f: Measured  $\pm$  200mV from steady state output voltage.

## WRITE CYCLE 1: W CONTROLLED<sup>h</sup>

| NO.  | SYMBOL          | PARAMETER                            | 1420 | )L-70 |     | )L-10 | UNITS | NOTES |

|------|-----------------|--------------------------------------|------|-------|-----|-------|-------|-------|

| 110. | OTWOOL          |                                      | MIN  | MAX   | MIN | MAX   |       | NOTED |

| 11   | t <sub>wc</sub> | Write Cycle Time                     | 70   |       | 100 |       | ns    |       |

| 12   | t <sub>wP</sub> | Write Pulse Width                    | 65   |       | 70  |       | ns    |       |

| 13   | t <sub>cw</sub> | Chip Enable to End of Write          | 65   |       | 70  |       | ns    |       |

| 14   | t <sub>DW</sub> | Data Set-up to End of Write          | 30   |       | 35  |       | ns    |       |

| 15   | t <sub>DH</sub> | Data Hold After End of Write         | 5    |       | 5   |       | ns    |       |

| 16   | t <sub>AW</sub> | Address Set-up to End of Write       | 65   |       | 70  |       | ns    |       |

| 17   | t <sub>AS</sub> | Address Set-up to Beginning of Write | 0    |       | 0   |       | ns    |       |

| 18   | t <sub>wR</sub> | Address Hold After End of Write      | 5    |       | 5   |       | ns    |       |

| 19   | t <sub>wz</sub> | Write Enable to Output Disable       |      | 35    |     | 40    | ns    | f     |

| 20   | t <sub>ow</sub> | Output Active After End of Write     | 0    |       | 0   |       | ns    | g     |

Note f: Measured ± 200mV from steady state output voltage. Note g: If  $\overline{E}$  goes low with  $\overline{W}$  low, output remains in high impedance state. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{IH}$  during address transitions.

## WRITE CYCLE 2: E CONTROLLED<sup>h</sup>

| NO. | SYMBOL          | PARAMETER                            | 1420 | )L-70 | 1420 | )L-10 | UNITS | NOTES |

|-----|-----------------|--------------------------------------|------|-------|------|-------|-------|-------|

|     | OTMOOL          |                                      | MIN  | MAX   | MIN  | MAX   |       |       |

| 21  | t <sub>wc</sub> | Write Cycle Time                     | 70   |       | 100  |       | ns    |       |

| 22  | t <sub>wP</sub> | Write Pulse Width                    | 65   |       | 70   |       | ns    |       |

| 23  | t <sub>cw</sub> | Chip Enable to End of Write          | 65   |       | 70   |       | ns    |       |

| 24  | t <sub>DW</sub> | Data Set-up to End of Write          | 30   |       | 35   |       | ns    |       |

| 25  | t <sub>DH</sub> | Data Hold After End of Write         | 5    |       | 5    |       | ns    |       |

| 26  | t <sub>AW</sub> | Address Set-up to End of Write       | 60   |       | 65   |       | ns    |       |

| 27  | t <sub>wR</sub> | Address Hold After End of Write      | 5    |       | 5    |       | ns    |       |

| 28  | t <sub>AS</sub> | Address Set-up to Beginning of Write | -5   |       | -5   |       | ns    |       |

| 29  | t <sub>wz</sub> | Write Enable to Output Disable       |      | 35    |      | 40    | ns    | f     |

Note f: Measured ± 200mV from steady state output voltage. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\ge V_{\text{IH}}$  during address transitions.

### IMS1400L

### **DEVICE OPERATION**

The IMS1400L has two control inputs: Chip Enable (E) and Write Enable (W), 14 address inputs, a data in ( $D_{IN}$ ) and a data out ( $D_{OUT}$ ).

When  $V_{CC}$  is first applied to pin 20, a circuit associated with the  $\overline{E}$  input forces the device into the lower power standby mode regardless of the state of the  $\overline{E}$  input. After  $V_{CC}$  is applied for 2ms, the  $\overline{E}$  input controls device selection as well as active and standby modes.

With E low, the device is selected and the 14 address inputs are decoded to select one memory cell out of 16,385. READ and WRITE operations on the memory cell are controlled by  $\overline{W}$  input. With  $\overline{E}$  high, the device is deselected, the output is disabled, and the power consumption is reduced to less than one-fifth of the active mode power.

#### **READ CYCLE**

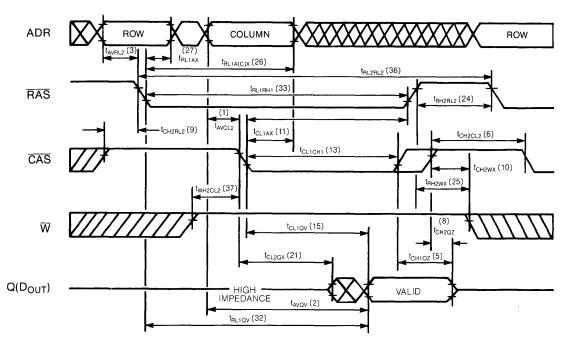

A read cycle is defined as  $\overline{W} \ge V_{IH}$  min with  $\overline{E} \le V_{IL}$  max. Read access time is measured from either  $\overline{E}$  going low or from valid address.

The READ CYCLE 1 waveform on page 3 shows a read access that is initiated by a change in the address inputs while  $\overline{E}$  is low. The output remains active throughout a READ CYCLE 1 and is valid at the specified address access time. As long as  $\overline{E}$  remains low, the cycle time is equal to the address access time.

The READ CYCLE 2 waveform on page 3 shows a read access that is initiated by  $\overline{E}$  going low. As long as address is stable within 5ns after  $\overline{E}$  goes low, valid data is at the output at the specified Chip Enable access time. If address is not valid within 5ns after  $\overline{E}$  goes low,

the timing is as specified in the READ CYCLE 1. Chip Enable access time is not affected by the duration of the deselect interval.

### WRITE CYCLE

A write cycle is initiated by the latter of  $\overline{W}$  or  $\overline{E}$  going low, and terminated by  $\overline{W}$  (WRITE CYCLE 1) or  $\overline{E}$ (WRITE CYCLE 2) going high. During the write cycle, data on the input ( $D_{\rm IN}$ ) is written into the selected cell, and the output ( $D_{\rm OUT}$ ) is in high impedance.

If a write cycle is initiated by W going low, the address must be stable for the WRITE CYCLE 1 set-up time. If a write cycle is initiated by E going low, the address must be held stable for the entire write cycle. After W or E goes high to terminate the cycle, addresses may change. If these address set-up and hold times are not met, contents of other cells may be altered in unpredictable wavs.

WRITE CYCLE 1 waveform on page 4 shows a write cycle terminated by  $\overline{W}$  going high.  $D_{IN}$  set-up and hold times are referenced to the rising edge of  $\overline{W}$ . With  $\overline{W}$  high,  $D_{OUT}$  becomes active.

WRITE CYCLE 2 waveform on page 5 shows a write cycle terminated by  $\overline{E}$  going high. D<sub>IN</sub> set-up and hold times are referenced to the rising edge of  $\overline{E}$ . With  $\overline{E}$  high, D<sub>OUT</sub> remains in the high impedance state.

### APPLICATION

To ensure proper operation of the IMS1400L in a system environment, it is recommended that the following guidelines on board layout and power distribution be followed.

Static RAMs

### POWER DISTRIBUTION

The recommended power distribution scheme combines proper power trace layout and placement of decoupling capacitors. The impedance in the decoupling path from the power pin (20) through the decoupling capacitor, to the ground pin (10) should be kept to a minimum. The impedance of this path is determined by the series impedance of the power line inductance and the inductance and reactance of the decoupling capacitor.

To reduce the power line impedance, it is recommended that the power trace and ground trace be gridded or provided by separate power planes. The high frequency decoupling capacitor should have a value of  $0.1\mu$ F, and be placed between the rows of memory devices in the array (see drawing). A larger tantalum

DECOUPLING CAPACITORS

capacitor with a value between  $22\mu$ F and  $47\mu$ F should be placed near the memory board edge connection where the power traces meet the backplane power distribution system. These large capacitors provide bulk energy storage to prevent voltage drop due to the main supply being located off the memory board and at the end of a long inductive path.

Also, to prevent loss of signal margins due to differential ground noise, the ground grid of the memory array should be extended to the TTL drivers in the peripheral circuitry.

### TERMINATION

Trace lines on a memory board in the array look to TTL driver signals like low impedance, unterminated transmission lines. In order to reduce or eliminate the reflections of the TTL signals, line termination is recommended. The termination may be either parallel or series but the series termination technique has the advantages of drawing no DC current and using a minimum of components. The recommended technique is to use series termination.

A series resistor in the signal line at the output of the TTL driver to match the source impedance of the TTL driver to the signal line will dampen the reflections on the line. The line should be kept short with the driver-termination combination close to the memory array.

Some experimentation will have to be done to find the proper value to use for the series termination to minimize reflections, but generally a series resistor in the  $10\Omega$  to  $30\Omega$  range will be required.

The use of proper power distribution techniques, including adequate use of decoupling capacitors, along with proper termination of TTL driver outputs, are some of the most important, yet basic rules to be followed.

The rules are intended to maintain the operating margins of all devices on the memory board by providing a quiet environment relatively free of noise spikes and signal reflections.

### **IMS1400L**

### **ORDERING INFORMATION**

| DEVICE   | SPEED | PACKAGE     | PART NUMBER  |

|----------|-------|-------------|--------------|

| IMS1400L | 70ns  | PLASTIC DIP | IMS1400P-70L |

|          | 100ns | PLASTIC DIP | IMS1400P-10L |

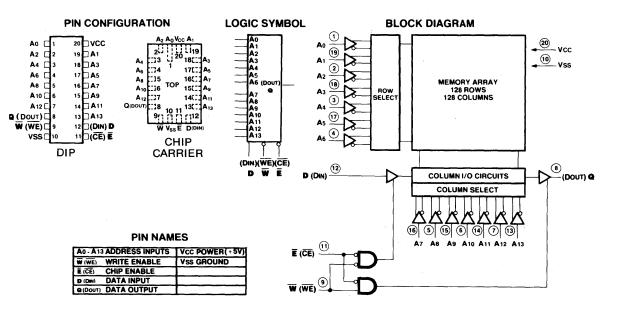

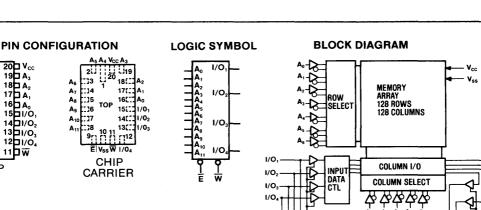

## IMS1420 **IMS1421 High Performance** 4K x 4 Static RAM

### FEATURES

IMS1420

IMS1421

- 4K x 4 Bit Organization

- 40nsec and 50nsec Address Access Times

- 605mW Maximum Power Dissipation

- Fully TTL Compatible

- Common Data Inputs & Outputs

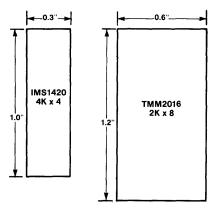

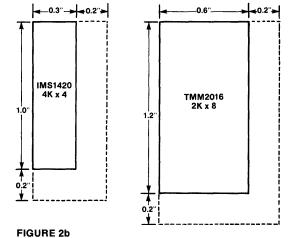

- 20-Pin, 300-mil DIP

- Single +5 volt ± 10% Operation

- 45nsec and 55nsec Chip Enable Access Times

- Power Down Function

- 165mW Maximum Standby Power

- High Speed Chip Select Function

- 30nsec and 40nsec Chip Select Access Times

### DESCRIPTION

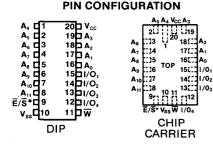

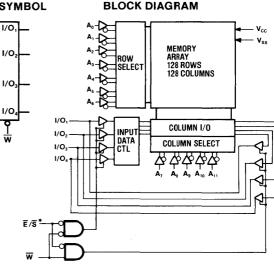

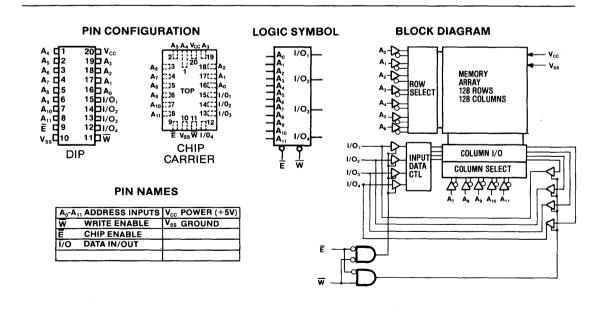

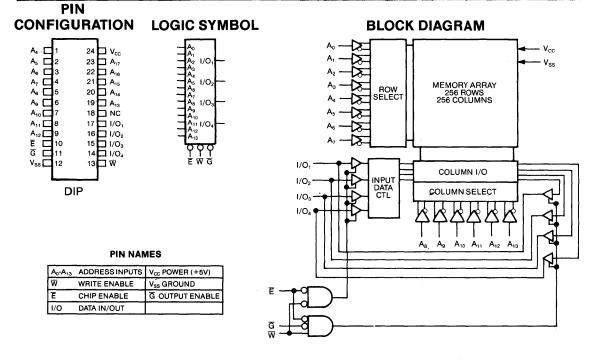

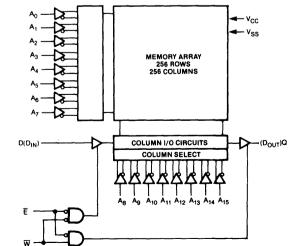

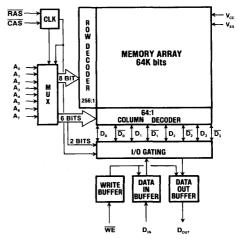

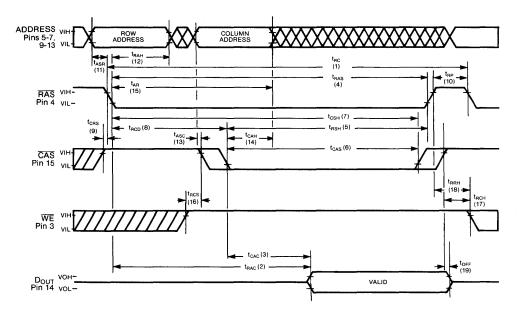

The IMS1420 and IMS1421 feature fully static operation requiring no external clocks or timing strobes, and equal address access and cycle times. Additionally, the IMS1420 provides a Chip Enable ( $\overline{E}$ ) function that can be used to place the device into a low-power standby mode, thus reducing power to 165mW. In place of the Chip Enable function, the IMS1421 provides a high speed Chip Select  $(\overline{S})$  function which allows faster access times to be achieved. With these two options, the designer can select the device which better fits his particular application.

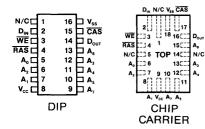

The IMS1420 is packaged in a 20-pin 300-mil plastic DIP and both the IMS1420 and IMS1421 are available in ceramic DIPs and ceramic chip carriers.

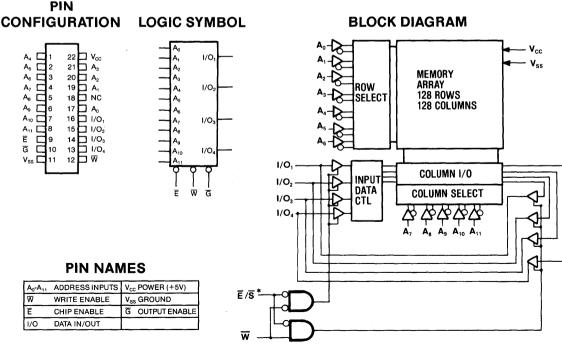

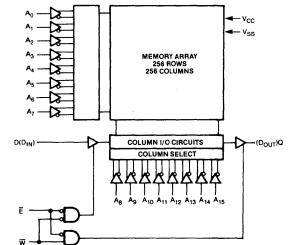

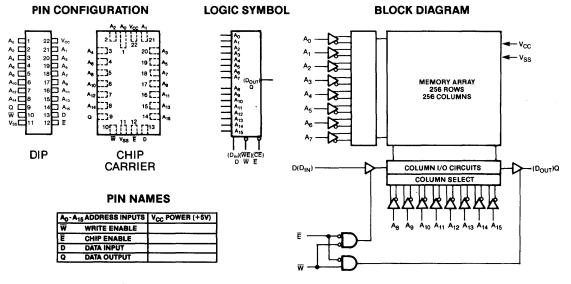

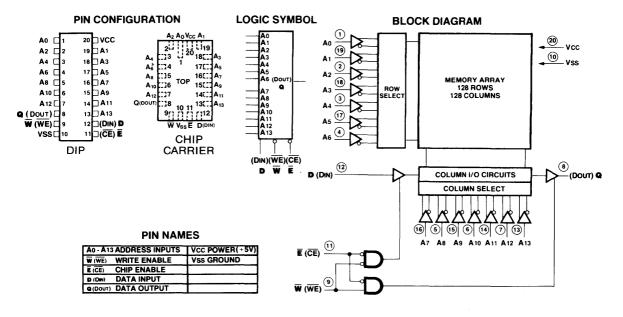

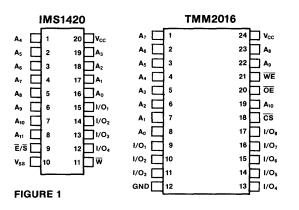

### **PIN NAMES**

| A <sub>0</sub> -A | ADDRESS INPUTS | V <sub>cc</sub> POWER (+5V) |

|-------------------|----------------|-----------------------------|

| Ŵ                 | WRITE ENABLE   | V <sub>ss</sub> GROUND      |

| Ē*                | CHIP ENABLE    |                             |

| <u>s</u> *        | CHIP SELECT    |                             |

| 1/0               | DATA IN/OUT    |                             |

\* E IMS1420 ONLY **S IMS1421 ONLY**  LOGIC SYMBOL

A3 A4 A6 A6 A7 A8

E/S

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to V <sub>SS</sub> | 3.5 to 7.0V    |

|------------------------------------------------|----------------|

| Temperature Under Bias.                        | -55°C to 125°C |

| Storage Temperature (Ambient)                  | -65°C to 150°C |

| Power Dissipation.                             | 1W             |

| DC Output Current                              |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **DC OPERATING CONDITIONS**

### TYPICAL DYNAMIC ICC VS TEMPERATURE

| SYMBOL           | PARAMETER                     | MIN  | ТҮР | MAX | UNITS | NOTES                                 |

|------------------|-------------------------------|------|-----|-----|-------|---------------------------------------|

| _V <sub>cc</sub> | Supply Voltage                | 4.5  | 5.0 | 5.5 | V     |                                       |

| V <sub>SS</sub>  | Supply Voltage                | 0 -  | 0   | 0   | V     |                                       |

| V <sub>IH</sub>  | Input Logic "1" Voltage       | 2.0  |     | 6.0 | V     |                                       |

| V <sub>IL</sub>  | Input Logic "0" Voltage       | -2.5 |     | 0.8 | V     |                                       |

| T <sub>A</sub>   | Ambient Operating Temperature | 0    |     | 70  | °C    | 400 Linear ft/min transverse air flow |

### DC ELECTRICAL CHARACTERISTICS (0°C $\leq$ T\_A $\leq$ +70°C) (V\_{cc} = 5.0V $\pm$ 10%)

| OVMDOL           |                                                     |     | 20  |     | 21  |       | NOTES                                                                          |

|------------------|-----------------------------------------------------|-----|-----|-----|-----|-------|--------------------------------------------------------------------------------|

| SYMBOL           | PARAMETER                                           | MIN | MAX | MIN | MAX | UNITS | NOTES                                                                          |

| I <sub>CC1</sub> | Average V <sub>CC</sub> Power Supply<br>Current AC  |     | 110 |     | 110 | mA    | $t_{\rm C} = t_{\rm C}$ (min)                                                  |

| I <sub>CC2</sub> | V <sub>CC</sub> Power Supply Current (Stdby)        |     | 30  |     | NA  | mA    | $\overline{E} \ge V_{H}$ (min)                                                 |

| l <sub>in</sub>  | Input Leakage Current<br>(Any Input)                |     | 10  |     | 10  | μΑ    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                |

| I <sub>olk</sub> | Off State Output<br>Leakage Current                 |     | 50  |     | 50  | μΑ    | V <sub>CC</sub> = max<br>V <sub>OUT</sub> = V <sub>SS</sub> to V <sub>CC</sub> |

| V <sub>OH</sub>  | Output Logic "1" Voltage<br>I <sub>out</sub> = -4mA | 2.4 |     | 2.4 |     | V     |                                                                                |

| V <sub>OL</sub>  | Output Logic "0" Voltage<br>I <sub>out</sub> = 8mA  |     | .4  |     | .4  | V     |                                                                                |

### **AC TEST CONDITIONS**<sup>a</sup>

| Input Pulse Levels                       |

|------------------------------------------|

| Input Rise and Fall Times 5ns            |

| Input and Output Timing Reference Levels |

| Output Load                              |

Note a: Operation to specifications guaranteed 2ms after  $V_{\mbox{CC}}$  applied.

### **CAPACITANCE** $^{\text{b}}$ (T<sub>A</sub> = 25°C, f = 1.0MHz)

| SYMBOL            | PARAMETER          | MAX | UNIT | CONDITIONS           |

|-------------------|--------------------|-----|------|----------------------|

| C <sub>IN</sub>   | Input Capacitance  | 4   | pF   | $\Delta V = 0$ to 3V |

| C <sub>OUT</sub>  | Output Capacitance | 7   | pF   | $\Delta V = 0$ to 3V |

| C <sub>Ē/</sub> s | E/S Capacitance    | 6   | pF   | $\Delta V = 0$ to 3V |

Note b: This parameter is sampled and not 100% tested.

### FIGURE 1. OUTPUT LOAD

## **READ CYCLE**

| NO.      | SYMBOL           | PARAMETER                             | 142 | 0-45 | 142 | 0-55 | 142 | 1-40 | 142 | 1-50 | UNITS | NOTES |

|----------|------------------|---------------------------------------|-----|------|-----|------|-----|------|-----|------|-------|-------|

| <u> </u> | OTMIDUL          |                                       | MIN | MAX  | MIN | МАХ  | MIN | MAX  | MIN | MAX  |       | NOILS |

| 1        | t <sub>ACS</sub> | Chip Enable/Select Access Time        |     | 45   |     | 55   |     | 30   |     | 40   | ns    |       |

| 2        | t <sub>RC</sub>  | Read Cycle Time                       | 40  |      | 50  |      | 40  |      | 50  |      | ns    | с     |

| 3        | t <sub>AA</sub>  | Address Access Time                   |     | 40   |     | 50   |     | 40   |     | 50   | ns    | d     |

| 4        | t <sub>OH</sub>  | Output Hold After Address Change      | 3   |      | 3   |      | 3   |      | 3   |      | ns    |       |

| 5        | t <sub>lez</sub> | Chip Enable/Select to Output Active   | 20  |      | 20  |      | 20  |      | 20  |      | ns    |       |

| 6        | t <sub>HZ</sub>  | Chip Disable/Select to Output Disable |     | 20   |     | 25   |     | 20   |     | 25   | ns    | f     |

| 7        | t <sub>PU</sub>  | Chip Enable to Power Up               | 0   |      | 0   |      | NA  |      | NA  |      | ns    |       |

| 8        | t <sub>PD</sub>  | Chip Disable to Power Down            |     | 45   |     | 55   |     | NA   |     | NA   | ns    |       |

| 9        | t <sub>RCS</sub> | Read Command Set-Up Time              | -5  |      | -5  |      | -5  |      | -5  |      | ns    |       |

| 10       | t <sub>RCH</sub> | Read Command Hold Time                | -5  |      | -5  |      | -5  |      | -5  |      | ns    |       |

|          | t <sub>T</sub>   | Input Rise and Fall Times             |     | 50   |     | 50   |     | 50   |     | 50   | ns    | е     |

Static RAMs

Note c: For READ CYCLES 1 & 2,  $\overline{W}$  is high for entire cycle.

Note d: Device is continuously selected  $\overline{E}/\overline{S}$  low.

Note e: Measured between  $V_{\text{IL}}$  max and  $V_{\text{IH}}$  min.

Note f: Measured  $\pm$  200mV from steady state output voltage.

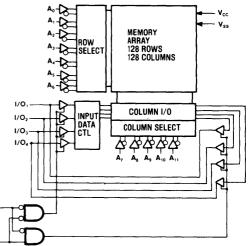

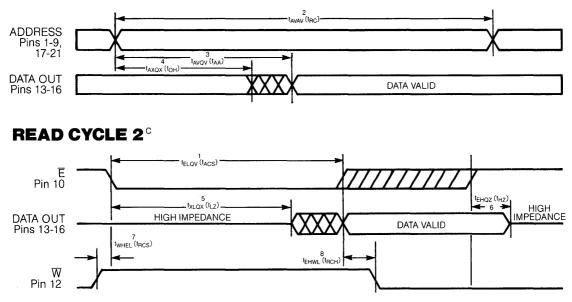

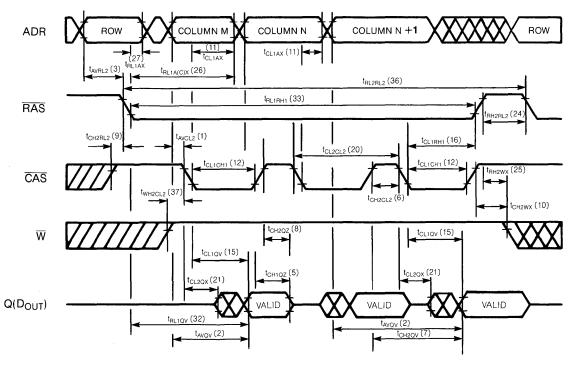

## READ CYCLE 1<sup>c,d</sup>

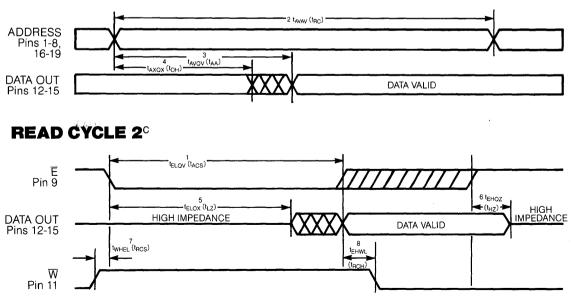

## **READ CYCLE 2**<sup>c</sup>

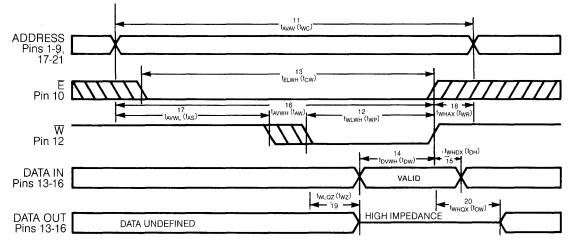

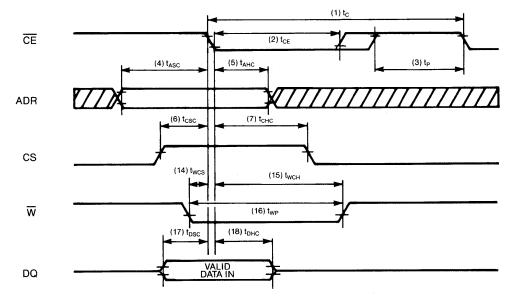

## WRITE CYCLE 1: W CONTROLLED<sup>h</sup>

| NO. | SYMBOL          | PARAMETER                            |     | 0-45 |     | 0-55 |     | 1-40 |     | 1-50 | UNITS | NOTES |

|-----|-----------------|--------------------------------------|-----|------|-----|------|-----|------|-----|------|-------|-------|

| NO. | STWIDOL         | FANAMETEN                            | MIN | MAX  | MIN | MAX  | MIN | MAX  | MIN | MAX  | UNITS | NOTES |

| 11  | t <sub>wc</sub> | Write Cycle Time                     | 40  |      | 50  |      | 40  |      | 50  |      | ns    |       |

| 12  | t <sub>wP</sub> | Write Pulse Width                    | 35  |      | 45  |      | 35  |      | 45  |      | ns    |       |

| 13  | t <sub>cw</sub> | Chip Enable/Select to End of Write   | 35  |      | 45  |      | 30  |      | 40  |      | ns    |       |

| 14  | t <sub>DW</sub> | Data Set-up to End of Write          | 15  |      | 20  |      | 15  |      | 20  |      | ns    |       |

| 15  | t <sub>DH</sub> | Data Hold After End of Write         | 3   |      | 3   |      | 3   |      | 3   |      | ns    |       |

| 16  | t <sub>AW</sub> | Address Set-up to End of Write       | 35  |      | 45  |      | 40  |      | 50  |      | ns    |       |

| 17  | t <sub>AS</sub> | Address Set-up to Beginning of Write | 0   |      | 0   |      | 0   |      | 0   |      | ns    |       |

| 18  | t <sub>wR</sub> | Address Hold After End of Write      | 5   |      | 5   |      | 0   |      | 0   |      | ns    |       |

| 19  | t <sub>wz</sub> | Write Enable to Output Disable       |     | 20   |     | 25   |     | 20   |     | 25   | ns    | f     |

| 20  | t <sub>ow</sub> | Output Active After End of Write     | 8   |      | 8   |      | 8   |      | 8   |      | ns    | g     |

Note f: Measured  $\pm$  200mV from steady state output voltage.

Note g: If  $\overline{E}/\overline{S}$  goes low with  $\overline{W}$  low, output remains in high impedance state. Note h:  $\overline{E}/\overline{S}$  or  $\overline{W}$  must be  $\geq V_{H}$  during address transitions.

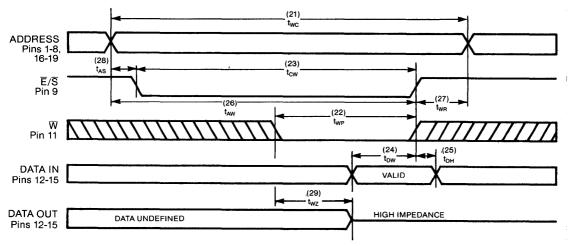

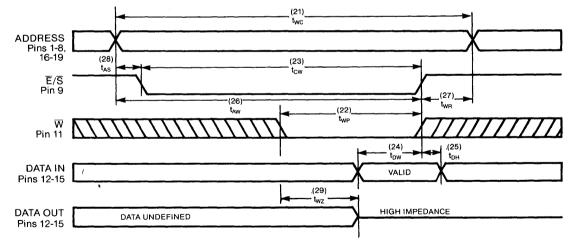

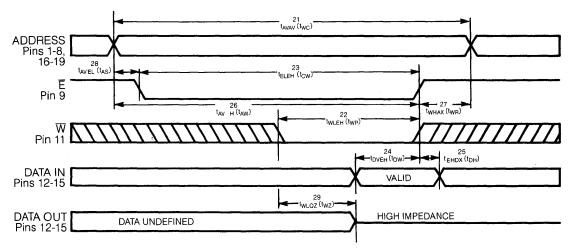

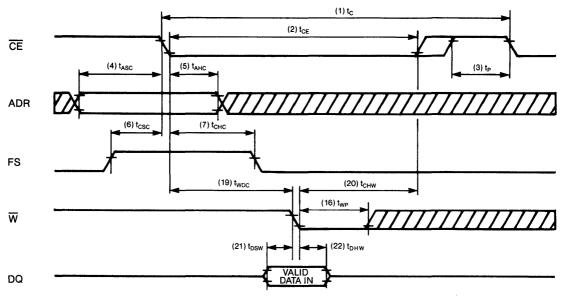

## WRITE CYCLE 2: E/S CONTROLLED<sup>h</sup>

| NO. | SYMBOL          | PARAMETER                            |    | 0-45 |    | 0-55 |    | 1-40 |    | 1-50 | UNITS | NOTES |

|-----|-----------------|--------------------------------------|----|------|----|------|----|------|----|------|-------|-------|

|     |                 |                                      |    | MAX  |    | MAX  |    | MAX  |    | MAX  |       |       |

| 21  | t <sub>wc</sub> | Write Cycle Time                     | 40 |      | 50 |      | 40 |      | 50 |      | ns    |       |

| 22  | t <sub>wP</sub> | Write Pulse Width                    | 35 |      | 45 |      | 35 |      | 45 |      | ns    |       |

| 23  | t <sub>cw</sub> | Chip Enable/Select to End of Write   | 35 |      | 45 |      | 30 |      | 40 |      | ns    |       |

| 24  | t <sub>DW</sub> | Data Set-up to End of Write          | 15 |      | 20 |      | 15 |      | 20 |      | ns    |       |

| 25  | t <sub>DH</sub> | Data Hold After End of Write         | 5  |      | 5  |      | 5  |      | 5  |      | ns    |       |

| 26  | t <sub>AW</sub> | Address Set-up to End of Write       | 30 |      | 40 |      | 35 |      | 45 |      | ns    |       |

| 27  | t <sub>wR</sub> | Address Hold After End of Write      | 5  |      | 5  |      | 5  |      | 5  |      | ns    |       |

| 28  | t <sub>AS</sub> | Address Set-up to Beginning of Write | -5 |      | -5 |      | 0  |      | 0  |      | ns    |       |

| 29  | t <sub>wz</sub> | Write Enable to Output Disable       |    | 20   |    | 25   |    | 20   |    | 25   | ns    | f     |

Note f:  $\underline{Measured} \pm 200 \text{mV}$  from steady state output voltage.

Note h:  $\overline{E}/\overline{S}$  or  $\overline{W}$  must be  $\geq V_{IH}$  during address transitions.

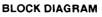

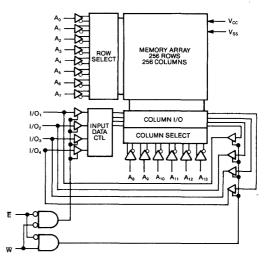

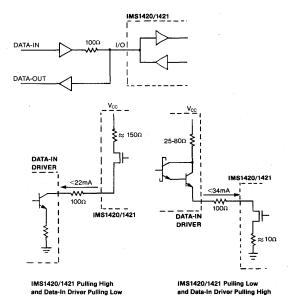

#### **DEVICE OPERATION (IMS1420)**

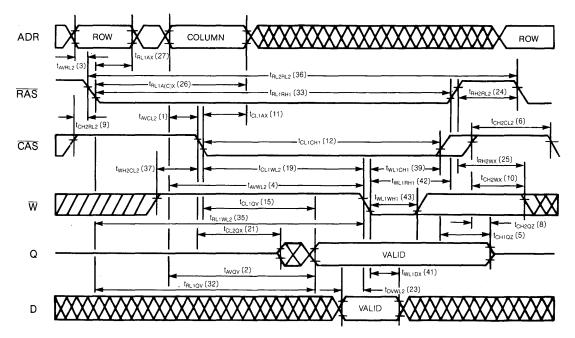

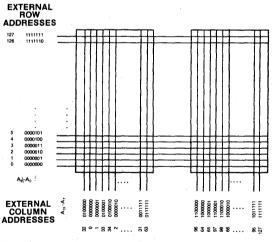

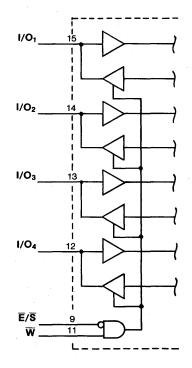

The IMS1420 has two control inputs, Chip Enable ( $\overline{E}$ ) and Write Enable ( $\overline{W}$ ), twelve address inputs, and four Data I/O lines.

When  $V_{CC}$  is first applied to pin 20, a circuit associated with the  $\overline{E}$  input forces the device into the lower power standby mode regardless of the state of the  $\overline{E}$  input. After  $V_{CC}$  is applied for 2ms, the  $\overline{E}$  input controls device selection as well as active and standby modes.

With  $\overline{E}$  low, the device is selected and the twelve address inputs are decoded to select one 4-bit word out of 4096. Read and Write operations on the memory cell are controlled by  $\overline{W}$  input. With  $\overline{E}$  high, the device is deselected, the output is disabled, and the power consumption is reduced to less than one-third of the active mode power.

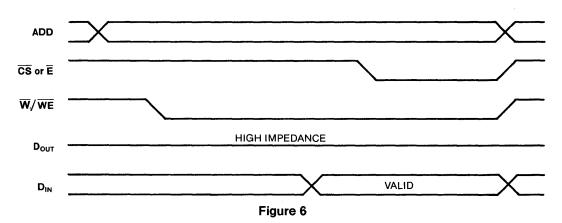

#### **READ CYCLE**

A read cycle is defined as  $\overline{W} \ge V_{\text{IH}}$  min with  $\overline{E} \le V_{\text{IL}}$  max. Read access time is measured from either  $\overline{E}$  going low or from valid address.

The READ CYCLE 1 waveform on page 3 shows a read access that is initiated by a change in the address inputs while E is low. The output remains active throughout READ CYCLE 1 and is valid at the specified address access time. The address inputs may change at access time and the output remains valid for a minimum of 3ns. As long as E remains low, the cycle time is equal to the address access time.

The READ CYCLE 2 waveform on page 3 shows a read access that is initiated by Egoing low. As long as address is stable within 5ns after E goes low, valid data is at the

output at the specified Chip Enable access time. If address is not valid within 5ns after  $\overline{E}$  goes low, the timing is as specified in READ CYCLE 1. Chip Enable access time is not affected by the duration of the deselect interval.

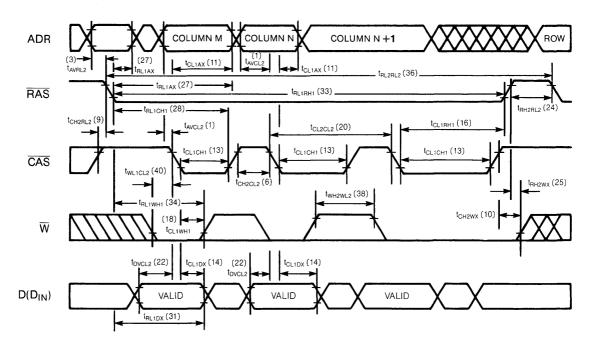

### WRITE CYCLE

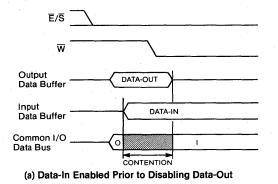

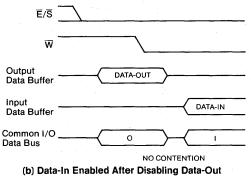

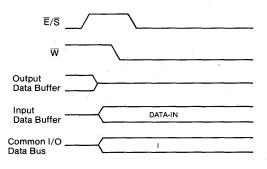

A write cycle is initiated by the latter of  $\overline{W}$  or  $\overline{E}$  goinc low, and terminated by  $\overline{W}$  (WRITE CYCLE 1) or  $\overline{E}$  (WRITE CYCLE 2) going high. During the write cycle, data on the inputs is written into the selected cells, and the outputs are floating.

If a write cycle is initiated by  $\overline{W}$  going low, the address must be stable for the WRITE CYCLE 1 set-up time. If a write cycle is initiated by  $\overline{E}$  going low, the address neec not be stable until a maximum of 5ns after  $\overline{E}$  goes low The address must be held stable for the entire write cycle After  $\overline{W}$  or  $\overline{E}$  goes high to terminate the write cycle addresses may change. If these address set-up and holc times are not met, contents of other cells may be alterec in unpredictable ways.

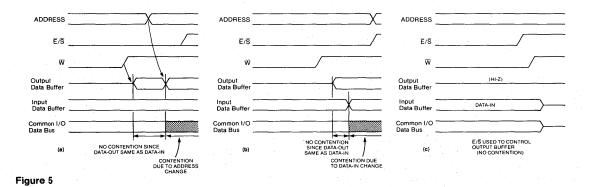

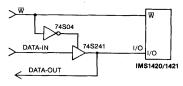

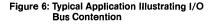

WRITE CYCLE 1 waveform on page 4 shows a write cycle terminated by  $\overline{W}$  going high. Data set-up and hole times are referenced to the rising edge of  $\overline{W}$ . With  $\overline{W}$  high, the outputs become active. When  $\overline{W}$  goes high a the end of a write cycle and the outputs of the memory geactive, the data from the memory will be the same as the data just written into the memory. Thus, no data bus contention will occur.

WRITE CYCLE 2 waveform on page 5 shows a write cycle terminated by  $\overline{E}$  going high. Data set-up and hold times are referenced to the rising edge of  $\overline{E}$ . With  $\overline{E}$  high the outputs remain in the high impedance state.

### **DEVICE OPERATION (IMS1421)**

The operation of the IMS1421 is similar to the operation of the IMS1420 except that the Chip Enable  $(\overline{E})$ function on the IMS1420 is replaced by a high speed Chip Select ( $\overline{S}$ ) for the IMS1421. The  $\overline{S}$  function controls chip selection but there is no power down function on the IMS1421. The IMS1421 is designed to allow even higher system performance than is possible with the IMS1420 by removing the Chip Select decoder delay from the critical access delay path.

With  $\overline{S}$  high, the device is deselected and the outputs are disabled

### **READ CYCLE**

A read cycle is defined as  $\overline{W} \ge V_{\text{IH}}$  min with  $\overline{S} \le V_{\text{IL}}$  max. Read access time is measured from either  $\overline{S}$  going low or from valid address. If  $\overline{S}$  goes low within 10ns of address valid, access time is equal to address access time. If  $\overline{S}$  goes low later than 10ns after address valid, then access time is equal to Chip Select access time.

### WRITE CYCLE

A write cycle is initiated by the latter of  $\overline{W}$  or  $\overline{S}$  going low and is terminated by  $\overline{W}$  (WRITE CYCLE 1) or  $\overline{S}$  (WRITE CYCLE 2) going high. During a write cycle, the outputs are floated and the data on the inputs are written into the addressed memory cells.

If a write cycle is initiated by  $\overline{W}$  going low, the address must be stable for the specified  $\underline{W}$ RITE CYCLE 1 set-up time. If a write cycle is initiated by  $\overline{S}$  going low, the address must be stable for the specified WRITE CYCLE 2 set-up time. WRITE CYCLE 1 waveform on page 4 shows a write cycle terminated by  $\overline{W}$  going high. Data set-up and hold times are referenced to the rising edge of  $\overline{W}$ . With  $\overline{W}$ high and  $\overline{S}$  low, the outputs become active.

WRITE CYCLE 2 on page 5 shows a write cycle terminated by the rising edge of  $\overline{S}$ . Data set-up and hold times are referenced to the rising edge of  $\overline{S}$  and the outputs remain in the high impedance state.

Static RAMs

### APPLICATION

Fundamental rules in regard to memory board layout should be followed to ensure maximum benefit from the features offered by the IMS1420/21 Static RAM.

### POWER DISTRIBUTION

The recommended power distribution scheme combines proper power trace layout and placement of decoupling capacitors to maintain the operating margins of the IMS1420/21. The impedance in the decoupling path from the power pin (20) through the decoupling capacitor to the ground pin (10) should be kept to a minimum. The impedance of this path is determined by the series impedance of the power line inductance and the inductance and reactance of the decoupling capacitor.

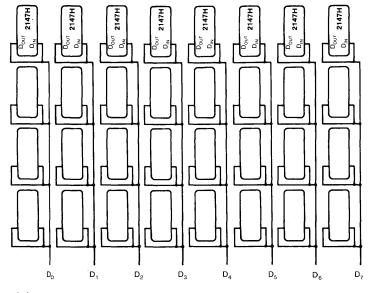

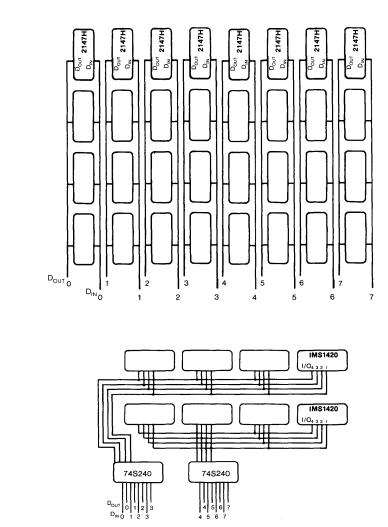

Since the current transients associated with the operation of the high speed IMS1420/21 are high frequency, the line inductance is the dominating factor. To reduce the line inductance, the power trace and ground trace should be gridded or provided by separate power planes. The decoupling capacitor acts as a low impedance power supply located near the memory device. The high frequency decoupling capacitor should have a value of  $0.1\mu$ F, and be placed between the rows of memory devices in the array (see drawing). A larger tantalum capacitor

V<sub>CC</sub>, V<sub>SS</sub> GRID SHOWING DECOUPLING CAPACITORS

with a value between  $22\mu$ F and  $47\mu$ F should be placed near the memory board edge connection where the power traces meet the back-plane power distribution system. These larger capacitors provide bulk energy storage to prevent voltage drop due to the main supply being located off the memory board and at the end of a long inductive path.

The ground grid of the memory array should extend to the TTL driver periphery circuit. This will provide a solid ground reference for the TTL drivers and prevent loss of operating margin of the drivers due to differential ground noise.

### TERMINATION

Trace lines on a memory board in the array look to TTL driver signals like low impedance, unterminated transmission lines. In order to reduce or eliminate the reflections of the TTL signals propagating down the lines, especially low going TTL signals, line termination is recommended. The termination may be either series or parallel.

The recommended technique is to use series termination. The series termination technique has the advantage of drawing no DC current and using a minimum of components. This is accomplished by placing a series resistor in the signal line at the output of the TTL driver to dampen the reflection on the line. The line should be kept short by placing the driver-termination combination close to the memory array.

Some experimentation will have to be done to find the proper value to use for the series termination to minimize reflections, but generally a series resistor in the  $10\Omega$  to  $30\Omega$  range will be required.

Proper power distribution techniques, including adequate use of decoupling capacitors, and proper termination of TTL drive outputs are some of the most important yet basic guidelines that need to be followed when designing and building a memory board. The guidelines are intended to maintain the operating margins of all devices on the memory board providing a quiet environment free of noise spikes and signal reflections.

### **ORDERING INFORMATION**

| DEVICE  | SPEED | PACKAGE      | PART NUMBER |

|---------|-------|--------------|-------------|

| IMS1420 | 45ns  | PLASTIC DIP  | IMS1420P-45 |

|         | 45ns  | CERAMIC DIP  | IMS1420S-45 |

|         | 45ns  | CHIP CARRIER | IMS1420W-45 |

|         | 55ns  | PLASTIC DIP  | IMS1420P-55 |

|         | 55ns  | CERAMIC DIP  | IMS1420S-55 |

|         | 55ns  | CHIP CARRIER | IMS1420W-55 |

| IMS1421 | 40ns  | CERAMIC DIP  | IMS1421S-40 |

|         | 40ns  | CHIP CARRIER | IMS1421W-40 |

|         | 50ns  | CERAMIC DIP  | IMS1421S-50 |

|         | 50ns  | CHIP CARRIER | IMS1421W-50 |

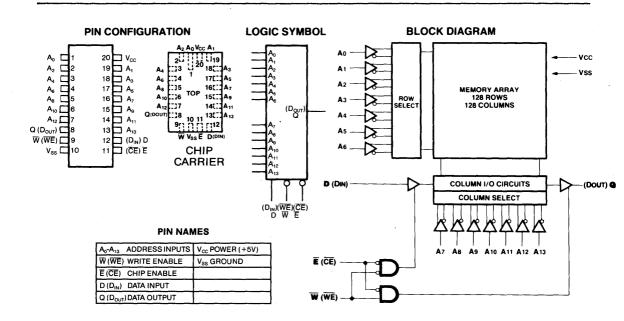

# IMS1420L Low Power 4Kx4 Static RAM

### FEATURES

- 4K x 4 Bit Organization

- 70 and 100ns Chip Enable Access Times

- 65 and 95ns Address Access Times

- 495mW Maximum Power Dissipation

- 83mW Maximum Standby Power

- Fully TTL Compatible

- Common Data Inputs and Outputs

- 20-pin, 300-mil Plastic DIP

- Single 5 volt ± 10% Operation

- Power Down Function

### DESCRIPTION

The INMOS IMS1420L features fully static operation requiring no external clocks or timing strobes, and equal address access and cycle times. Additionally, the IMS1420L provides a Chip Enable ( $\overline{E}$ ) function that can be used to place the device into a low-power standby mode, thus reducing power to 83mW.

The IMS1420L is packaged in a 20-pin, 300 mil plastic DIP. This makes possible high system packing densities.

The IMS1420L is a high speed VLSI RAM intended for applications that demand superior performance and reliability.

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to $V_{ss}$ |                |

|-----------------------------------------|----------------|

| Temperature Under Bias                  | -55°C to 125°C |

| Storage Temperature (Ambient)           |                |

| Power Dissipation.                      | 1W             |

| DC Output Current.                      |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **DC OPERATING CONDITIONS**

### TYPICAL DYNAMIC ICC VS TEMPERATURE

| SYMBOL          | PARAMETER                     | MIN  | ТҮР | МАХ | UNITS | NOTES                                 |

|-----------------|-------------------------------|------|-----|-----|-------|---------------------------------------|

| V <sub>cc</sub> | Supply Voltage                | 4.5  | 5.0 | 5.5 | V     |                                       |

| V <sub>SS</sub> | Supply Voltage                | 0    | 0   | 0   | ٧     |                                       |

| V <sub>IH</sub> | Input Logic "1" Voltage       | 2.0  |     | 6.0 | ٧     |                                       |

| VIL             | Input Logic "0" Voltage       | -2.5 |     | 0.8 | ۷     |                                       |

| T <sub>A</sub>  | Ambient Operating Temperature | 0    |     | 70  | °C    | 400 Linear ft/min transverse air flow |

### DC ELECTRICAL CHARACTERISTICS (0°C $\leq$ T\_A $\leq$ 70°C) (V\_{cc} = 5.0V $\pm$ 10%)

| SYMBOL           | PARAMETER                                         |          | MIN | МАХ | UNITS | NOTES                                            |

|------------------|---------------------------------------------------|----------|-----|-----|-------|--------------------------------------------------|

| I <sub>CC1</sub> | Average V <sub>cc</sub> Power                     | 0°C      |     | 90  |       |                                                  |

|                  | Supply Current AC                                 | 25°C     |     | 85  | mA    | $t_c = t_c min$                                  |

|                  |                                                   | 70°C     |     | 75  |       |                                                  |

| I <sub>CC2</sub> | V <sub>cc</sub> Power Supply Current<br>(Standby) | 0°C-70°C |     | 15  | mA    | $\overline{E} \ge V_{IH}$ min                    |

| l <sub>in</sub>  | Input Leakage Current<br>(Any Input)              |          |     | 10  | μA    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$  |

| ј <sub>оlк</sub> | Off State Output<br>Leakage Current               |          |     | 50  | μA    | $V_{CC} = max$<br>$V_{OUT} = V_{SS}$ to $V_{CC}$ |

| V <sub>OH</sub>  | Output Logic "1" Voltage Iout =                   | = -4mA   | 2.4 |     | V     |                                                  |

| V <sub>OL</sub>  | Output Logic "0" Voltage IOUT =                   | = 8mA    |     | 0.4 | V     |                                                  |

### **AC TEST CONDITIONS**<sup>a</sup>

| Input Pulse Levels |

|--------------------|

| Output Load        |

Note a: Operation to specifications guaranteed 2ms after  $V_{\mbox{CC}}$  applied.

### **CAPACITANCE** $^{\text{b}}$ (T<sub>A</sub> = 25°C, f = 1.0MHz)

| SYMBOL          | PARAMETER          | MAX | UNIT | CONDITIONS           |

|-----------------|--------------------|-----|------|----------------------|

| C <sub>IN</sub> | Input Capacitance  | 4   | рF   | $\Delta V = 0$ to 3V |

| COUT            | Output Capacitance | 7   | pF   | $\Delta V = 0$ to 3V |

| CE              | E Capacitance      | 6   | pF   | $\Delta V = 0$ to 3V |

Note b: This parameter is sampled and not 100% tested.

### FIGURE 1. OUTPUT LOAD

| NO. | SYMBOL              |                  | PARAMETER                        | 140 | 1400L-70 |     | 0L-10 | UNITE | NOTES |

|-----|---------------------|------------------|----------------------------------|-----|----------|-----|-------|-------|-------|

|     | Standard            | Alternate        | FANAMEIEN                        | MIN | MAX      | MIN | MAX   |       | NOIES |

| 1   | t <sub>ELQV</sub>   | t <sub>ACS</sub> | Chip Enable Access Time          |     | 70       |     | 100   | ns    |       |

| 2   | t <sub>AVAV</sub>   | t <sub>RC</sub>  | Read Cycle Time                  | 65  |          | 95  |       | ns    | с     |

| 3   | t <sub>AVQV</sub>   | t <sub>AA</sub>  | Address Access Time              |     | 65       |     | 95    | ns    | d     |

| 4   | t <sub>AXQX</sub>   | t <sub>он</sub>  | Output Hold After Address Change | 5   |          | 5   |       | ns    |       |

| 5   | t <sub>ELQX</sub>   | t <sub>LZ</sub>  | Chip Enable to Output Active     | 5   |          | 5   |       | ns    |       |

| 6   | t <sub>eHQZ</sub>   | t <sub>HZ</sub>  | Chip Disable to Output Disable   | 0   | 30       | 0   | 40    | ns    | f     |

| 7   | t <sub>ELICCH</sub> | t <sub>PU</sub>  | Chip Enable to Power Up          | 0   |          | 0   |       | ns    |       |

| 8   | t <sub>EHICCL</sub> | t <sub>PD</sub>  | Chip Disable to Power Down       | 0   | 65       | 0   | 65    | ns    |       |

|     |                     | t <sub>T</sub>   | Input Rise and Fall Times        |     | 50       |     | 50    | ns    | е     |

Note c: For READ CYCLES 1 & 2,  $\overline{W}$  is high for entire cycle.

Note d: Device is continuously selected  $\overline{E}$  low.

Note e: Measured between  $V_{IL}$  max and  $V_{IH}$  min.

Note f: Measured  $\pm$  200mV from steady state output voltage.

## READ CYCLE 1<sup>c, d</sup>

## **READ CYCLE 2**°

### RECOMMENDED AC OPERATING CONDITIONS ( $0^{\circ}C \le T_A \le 70^{\circ}C$ ) ( $V_{cc} = 5.0V \pm 10\%$ )

| NO. | SYMBOL            |                 | PARAMETER                            |     | 1400L-70 |     | 0L-10 | UNITS | NOTES |

|-----|-------------------|-----------------|--------------------------------------|-----|----------|-----|-------|-------|-------|

|     | Standard          | Alternate       | FANAWEIEN                            | MIN | MAX      | MIN | MAX   | UNITS | NOTES |

| 9   | t <sub>AVAV</sub> | t <sub>wc</sub> | Write Cycle Time                     | 65  |          | 95  |       | ns    |       |

| 10. | t <sub>wLWH</sub> | t <sub>wP</sub> | Write Pulse Width                    | 40  |          | 45  |       | ns    |       |

| 11  | t <sub>elwh</sub> | t <sub>cw</sub> | Chip Enable to End of Write          | 55  |          | 60  |       | ns    |       |

| 12  | t <sub>DVWH</sub> | t <sub>DW</sub> | Data Set-up to End of Write          | 30  |          | 35  |       | ns    |       |

| 13  | t <sub>wHDX</sub> | t <sub>DH</sub> | Data Hold After End of Write         | 0   |          | 5   |       | ns    |       |

| 14  | t <sub>avwh</sub> | t <sub>AW</sub> | Address Set-up to End of Write       | 55  |          | 60  |       | ns    |       |

| 15  | t <sub>AVWL</sub> | t <sub>AS</sub> | Address Set-up to Beginning of Write | 5   |          | 10  |       | ns    |       |

| 16  | t <sub>whax</sub> | t <sub>WR</sub> | Address Hold After End of Write      | 0   |          | 5   |       | ns    |       |

| 17  | t <sub>wLQZ</sub> | t <sub>wz</sub> | Write Enable to Output Disable       | 0   | 20       | 0   | 35    | ns    | f     |

| 18  | t <sub>wHQX</sub> | t <sub>ow</sub> | Output Active After End of Write     | 0   | 40       | 0   | 40    | ns    | g     |

## WRITE CYCLE 1: W CONTROLLED<sup>h</sup>

Note f: Measured ± 200mV from steady state output voltage.

Note g: If  $\overline{E}$  goes low with  $\overline{W}$  low, output remains in high impedance state. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{\rm IH}$  during address transitions.

## WRITE CYCLE 2: E CONTROLLED<sup>h</sup>

| NO. | SYMBOL            |                 | PARAMETER                            | 1400L-70 |     | 1400L-10 |     | UNITS | NOTES |